工具/软件:

尊敬的 TI 外设:

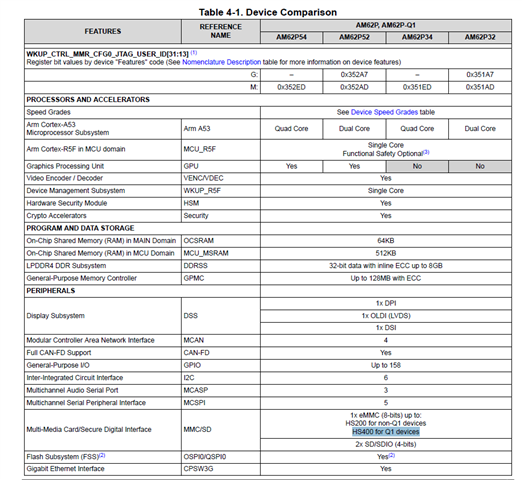

您能否提供有关 AM62P HS400 支持的信息。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的电路板设计人员:

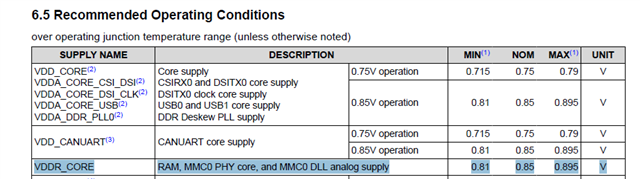

另一个建议是 在 0.85V 电压下运行 VDD_CORE 时、从与 VDD_CORE 相同的源获取 VDDR_CORE。 我不会看到从不同的源为 VDDR_CORE 供电的问题、只要这些源确保不存在 允许施加到 VDDR_CORE 的电势大于上电或断电期间施加到 VDD_CORE 的电势+ 0.18V 的工作条件。 我们建议客户在 0.85V 电压下运行 VDD_CORE 时为 VDDR_CORE 和 VDD_CORE 使用相同的源、以消除这一问题。

支持 HS400 的计划更新:

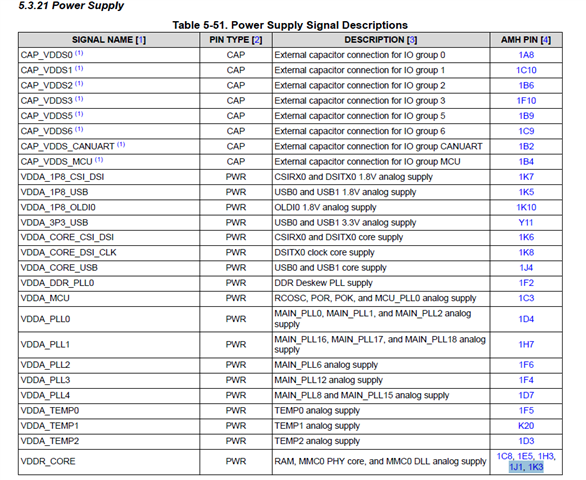

VDDA_0P85_DLL_MMC0 和 VDD_MMC0 电源轨分别连接到自己的引脚 1J1 和 1K3、将连接到与相同的网络

VDDR_CORE 电源轨来自引脚 1C8、1E5 和 1H3。 这一更改会 在封装内整合 VDDR_CORE、VDD_MMC0 和 VDDA_0P85_DLL_MMC0 电源轨、其中三个电源轨将共享引脚 1C8、1E5、1H3、1J1 和 1K3。 我计划为所有五个引脚分配名称“VDDR_CORE “、并更新信号说明以包含全部三个电源轨。

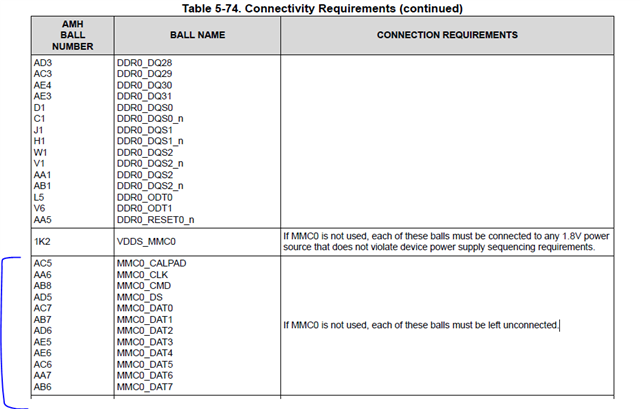

这种更改会给不使用 MMC0 的任何客户带来问题、他们连接了 VDDA_0P85_DLL_MMC0 和 VDD_MMC0 电源轨

电压下拉至与 VDD_CORE 相同的源、这是上一个数据表中的说明。 这种 PCB 连接会将 0.75V 和 0.85V 电源短接在一起

就可以通过我们的新软件包访问我们的新软件包。

这一变化也会给设计为使用两个 0.85V 电源的系统带来一个问题、而这个由一个 0.85V 电源供电

VDDA_0P85_DLL_MMC0 和 VDD_MMC0 电源轨、另一个 0.85V 电源为 VDDR_CORE 电源轨供电。

如果要安装新封装、这种 PCB 连接方式会通过我们的新封装将两个 0.85V 电源短接在一起。

原理图的建议更改

建议将 VDDA_0P85_DLL_MMC0 和 VDD_MMC0 电源轨连接到与 VDDR_CORE 连接的同一电源

布局指南

常见问题解答正在更新中。 请查看常见问题解答以了解更新信息。

注意:

TI.com 上提供了更新后的数据表

转换时间

此致、

Sreenivasa.

尊敬的电路板设计人员:

TI.com 上提供了更新后的数据表

转换时间

此致、

Sreenivasa.