工具/软件:

TI 团队大家好、

处理器: AM6442

SDK 版本: AM64x MCU+ SDK 11.00.00

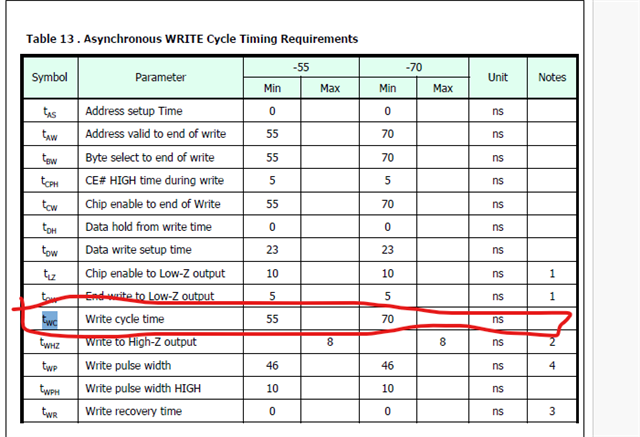

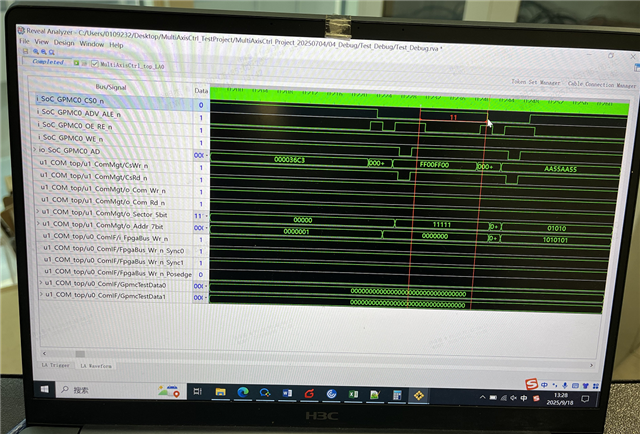

我目前正在使用 基于 AM6442 处理器 遵循我的习惯 视图 、侧重于通过 GPMC 实现 R5F 内核与 RAM 之间的通信。 当我在地址/数据多路复用器件上使用异步单次写入访问时、两个 nCS 信号之间的间隔时间(两次写入)为 11 个时钟周期(尽管我已经将 cycle2cycledelay 参数设置为 2)、我可以调整哪些参数以将时间间隔缩短为 2 个时钟周期。

请就此提供您的意见

谢谢。此致