工具/软件:

您好:

使用 TDA4 的 CPSW9G、port5-port8、其中 SGMII 连接到 phy 并成功 ping、port3、同时 RGMII 连接到 phy 芯片链路 、但我们无法 ping

SDK-10.01

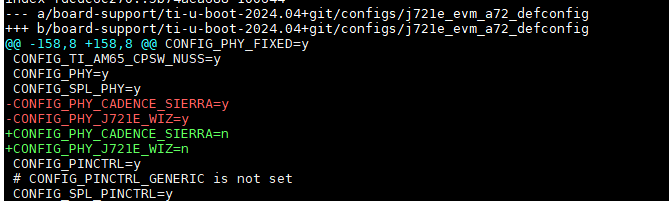

1. UBoot

2. Linux dts k3-j721e-common-proc-board.dts

rgmii3_default_pins: rgmii3-default-pins {

pinctrl-single,pins = <

J721E_IOPAD(0xb0, PIN_INPUT, 4) /* (AF28) PRG0_PRU0_GPO0.RGMII3_RD0 */

J721E_IOPAD(0xb4, PIN_INPUT, 4) /* (AE28) PRG0_PRU0_GPO1.RGMII3_RD1 */

J721E_IOPAD(0xb8, PIN_INPUT, 4) /* (AE27) PRG0_PRU0_GPO2.RGMII3_RD2 */

J721E_IOPAD(0xbc, PIN_INPUT, 4) /* (AD26) PRG0_PRU0_GPO3.RGMII3_RD3 */

J721E_IOPAD(0xc8, PIN_INPUT, 4) /* (AE26) PRG0_PRU0_GPO6.RGMII3_RXC */

J721E_IOPAD(0xc0, PIN_INPUT, 4) /* (AD25) PRG0_PRU0_GPO4.RGMII3_RX_CTL */

J721E_IOPAD(0xdc, PIN_OUTPUT, 4) /* (AJ28) PRG0_PRU0_GPO11.RGMII3_TD0 */

J721E_IOPAD(0xe0, PIN_OUTPUT, 4) /* (AH27) PRG0_PRU0_GPO12.RGMII3_TD1 */

J721E_IOPAD(0xe4, PIN_OUTPUT, 4) /* (AH29) PRG0_PRU0_GPO13.RGMII3_TD2 */

J721E_IOPAD(0xe8, PIN_OUTPUT, 4) /* (AG28) PRG0_PRU0_GPO14.RGMII3_TD3 */

J721E_IOPAD(0xf0, PIN_OUTPUT, 4) /* (AH28) PRG0_PRU0_GPO16.RGMII3_TXC */

J721E_IOPAD(0xec, PIN_OUTPUT, 4) /* (AG27) PRG0_PRU0_GPO15.RGMII3_TX_CTL */

>;

};

&cpsw0 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&rgmii3_default_pins>;

};

&cpsw0_port1 {

status = "disabled";

};

&cpsw0_port2 {

status = "okay";

phy-handle = <&cpsw9g_phy0>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 2>,<&serdes0_sgmii_link>;

//phy-names = "portmode", "serdes-phy";

phy-names = "portmode", "serdes";

};

&cpsw0_port3 {

status = "okay";

phy-handle = <&cpsw9g_phy13>;

phy-mode = "rgmii-rxid";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 3>;

};

&cpsw0_port4 {

status = "disabled";

};

&cpsw0_port5 {

status = "okay";

phy-handle = <&cpsw9g_phy1>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 5>,<&serdes4_sgmii_link>;

// phy-names = "portmode", "serdes-phy";

phy-names = "portmode", "serdes";

};

&cpsw0_port6 {

status = "okay";

phy-handle = <&cpsw9g_phy2>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 6>;

//phy-names = "portmode", "serdes-phy";

phy-names = "portmode", "serdes";

};

&cpsw0_port7 {

status = "okay";

phy-handle = <&cpsw9g_phy3>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 7>;

//phy-names = "portmode", "serdes-phy";

phy-names = "portmode", "serdes";

};

&cpsw0_port8 {

status = "okay";

phy-handle = <&cpsw9g_phy4>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 8>;

//phy-names = "portmode", "serdes-phy";

phy-names = "portmode", "serdes";

};

&cpsw9g_mdio {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&mdio0_pins_default>;

//reset-gpios = <&exp2 17 GPIO_ACTIVE_LOW>;

reset-post-delay-us = <120000>;

//bus_freq = <1000000>;

#address-cells = <1>;

#size-cells = <0>;

cpsw9g_phy0: ethernet-phy@4 {

reg = <4>;

};

cpsw9g_phy1: ethernet-phy@5 {

reg = <5>;

};

cpsw9g_phy2: ethernet-phy@8 {

reg = <8>;

};

cpsw9g_phy3: ethernet-phy@10 {

reg = <10>;

};

cpsw9g_phy4: ethernet-phy@12 {

reg = <12>;

};

cpsw9g_phy13: ethernet-phy@13 {

reg = <13>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

};

};

删除 j7-main-R5f0_0-fw

4.删除 uenv.txt 覆层

5. ethtool eth show link

root@j721e-evm:~# ethtool eth2

Settings for eth2:

Supported ports: [ TP MII ]

Supported link modes: 1000baseT/Full

Supported pause frame use: Symmetric

Supports auto-negotiation: No

Supported FEC modes: Not reported

Advertised link modes: Not reported

Advertised pause frame use: Symmetric

Advertised auto-negotiation: No

Advertised FEC modes: Not reported

Speed: 1000Mb/s

Duplex: Full

Auto-negotiation: off

Port: Twisted Pair

PHYAD: 13

Transceiver: external

MDI-X: Unknown

Supports Wake-on: d

Wake-on: d

Current message level: 0x000020f7 (8439)

drv probe link ifdown ifup rx_err tx_err hw

Link detected: yes

root@j721e-evm:~#

root@j721e-evm:~#

6. RGMII 链路、Ω、但无法 ping

root@j721e-evm:/home/weston/scripts# ./j7_devmem2_cpsw9g_check_status.sh

Platform: J7 TDA4VM

Command: k3conf

MDIO_ALIVE_REG (0x0c000f08) = 0x00000000

MDIO_LINK_REG (0x0c000f0c) = 0x00000000

please input your port: 1-8 3

CTRLMMR_ENET 3 CTRL (0x0010404c) = 0x00000002

PORT_MODE_SEL : 2h RGMII

RGMII_ID_MODE : 0h Internal Transmit Desaly

CPSW SS RGMII 3 STATUS (0x0c000038) = 0x0000000D

FULLDUPLEX : 1h Full duplex

SPEED : 1000Mbps

LINK : 1h Link is up

CPSW_SS_STATUS_SGMII_LINK_REG (0x0c000078) = 0x00000000

SGMII1_LINK : 0h No

CPSW_SS_SGMII_CONTROL_REG_ 3 (0x0c000310) = 0x00000000

TEST_PATTERN_EN : 0h operation

MASTER : 0h Slave Mode

LOOPBACK : 0h Not in internal loopback mode

MR_NP_LOADED : 0h --------

FAST_LINK_TIMER : 0h link timer 10ms in FIBER mode and 1.6ms in SGMII mode

MA_AN_RESTART : 0h Write 1h and tehn 0h to this bit caused the auto negotiation

MR_AN_ENABLE : 0h wirte 1 to this bit enbales the auto negotiation progess

CPSW_SS_SGMII_STATUS_REG_ 3 (0x0c000314) = 0x00000028

LOCK : 0h SEDES PLL isn't locked

MR_AN_COMPLETE : 0h no AUTO Negotiation is not complete

AN_EEROR : 0h no negotiation error

LINK : 0h link is not up

root@j721e-evm:/home/weston/scripts#