工具/软件:

我正在开发定制设计、并查看参考设计 PROC114E3。 我使用类似的 DDR4 存储器 IC。

我已经审阅并记录了原理图和原理图、然后我尝试将一些内容拼接在一起。

查看 sprad06c。

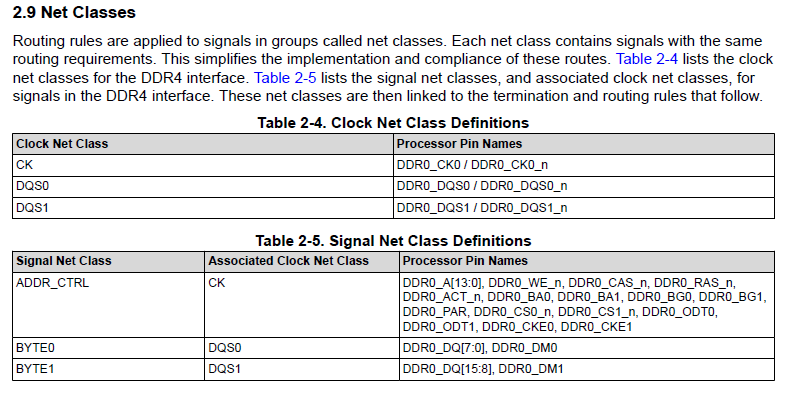

据我所知、DDR4 存储器定义了网类别和信号。

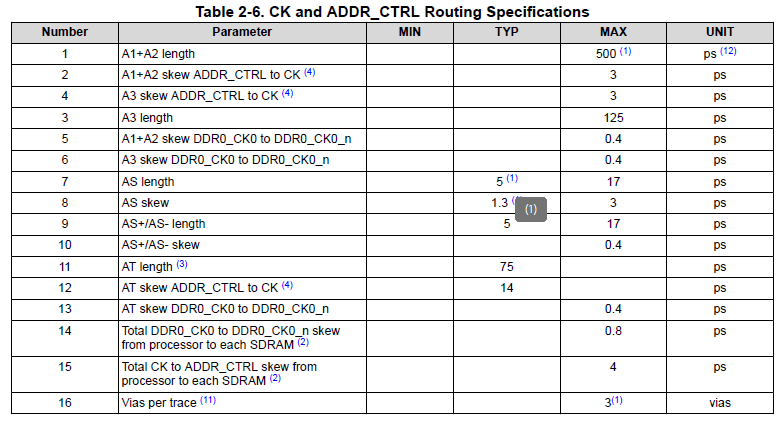

我的解释是、所示的 ADDR_CTRL 线的长度应与所示的 CK 线一致。

此外、这些电缆的长度应与更远的距离匹配。 指南指出 A13 可能是最远的。

但是、根据 PROC1143E 的 IC 方向、两个 CK 引脚距离处理器最远。

布线指南提供了最大延迟时间。

它指出: 使用长度匹配(以 mil 为单位)而不是延时时间(以 ps 为单位)、将延时时间(以 ps 为单位)乘以 5。

地址线最高可达 2500mil。

我回顾上述设计时、两条时钟线的运行长度均为 1492mil。

我读取了上面的第 2 行、ADDR 和 CK 之间的偏差需要为 3ps 或 15mil。

但在查看地址线时、它们与时钟线不匹配、它们不在时钟线的 15mil (3ps) 范围内。

A0:1392 密耳

A1:1391 密耳

...

A13: 1395 密耳

表 2-5 中的其他项目也不完全相同:

BA0:1316 密耳

Ba1:1316 密耳

ODT:1296 密耳

我有什么误解?