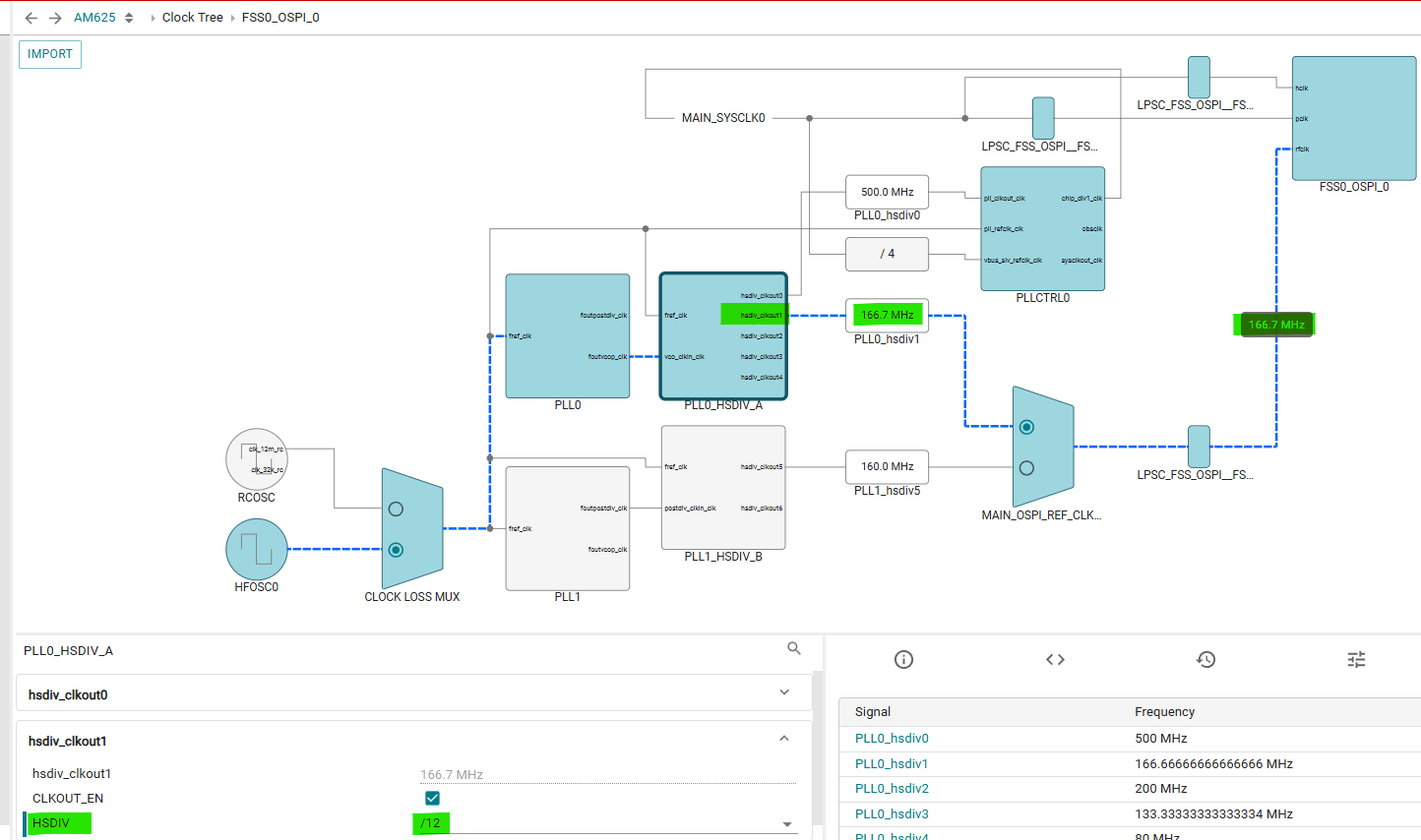

Thread 中讨论的其他器件:UNIFLASH、 SYSCONFIG

工具/软件:

代表客户发帖。

我们在该项目中面临着紧迫的问题。 在我们的耐久性测试中、我们遇到了很多常见的 PHY 调优问题。

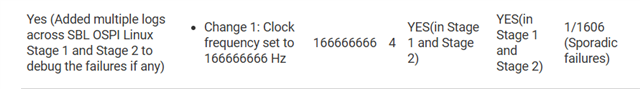

最初我们看到了单次发生、但在添加更多调试日志后、我们能够连续重现数百个 PHY 调优故障链(导致启动过程重新启动)。 重试几小时的 PHY 调优后(因此至少硬件并不会失效)。

此外,与此相关的是,在同一个测试中,我们重现了频繁的垃圾收集问题,指出了一般的闪存问题。

我们添加了日志并重现了该问题。 当我们无法写入闪存时、dmesg 显示:

SPI-NOR spi0.0:发生编程错误

在我们拥有的所有 RAM 配置中、这两个问题都可在多个器件上重现。

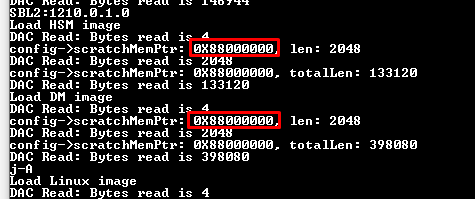

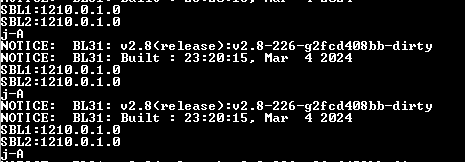

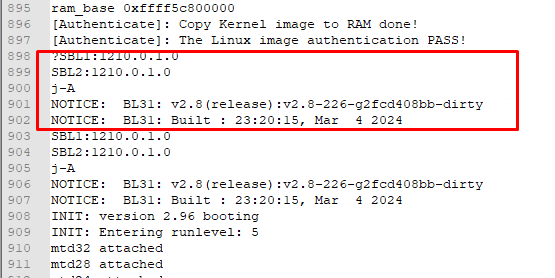

该模式如下所示、并发生在 R5 上的 SBL 第二阶段 (SBL2) 中:

[2025-06-06 07:47:09.614] SBL1:1210.0.1.0 [2025-06-06 07:47:09.721] SBL2:1210.0.1.0 [2025-06-06 07:47:09.721] ReadData prog_req_flag fail [2025-06-06 07:47:09.756] ERROR: Flash_norOspi_enablePhy:1222: Flash_norOspi_enablePhy : PHY enabling failed!!! Continuing without PHY... [2025-06-06 07:47:09.858] SBL1:1210.0.1.0 [2025-06-06 07:47:09.949] SBL2:1210.0.1.0 [2025-06-06 07:47:10.011] j-A [2025-06-06 07:47:10.243] NOTICE: BL31: v2.8(release):v2.8-226-g2fcd408bb-dirty [2025-06-06 07:47:10.259] NOTICE: BL31: Built : 23:20:15, Mar 4 2024 [2025-06-06 07:47:10.871] INIT: version 2.96 booting

如果发生问题、我们会重新启动器件、因此我们没有机会查看它是否会在 Linux 中仍然是一个问题。