工具/软件:

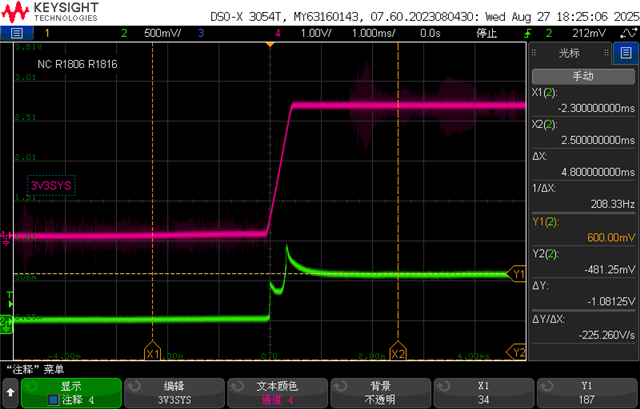

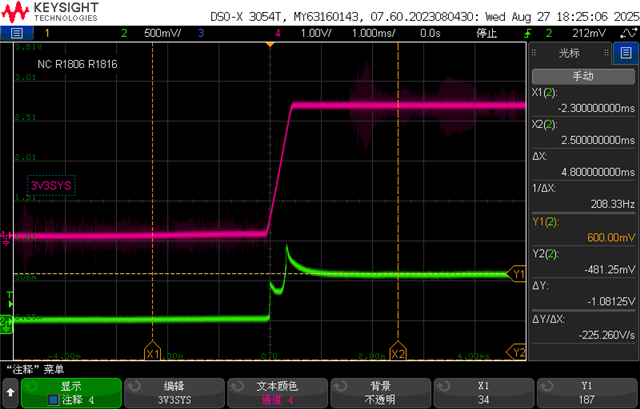

在测试 AM62A7 的引脚时、我们发现、在 AB20 上电(在 3V3 域中用作 GPIO)时、VCC3V3_SYS 将有大约 0.6V 的阶跃。 波形如下图。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Sreenivasa

根据前面的答复、为该 IO 提供一个 1K Ω 的外部下拉电阻。 阶跃电压可降至 0.2V。 同时、在 AM62A 上电后、将该 IO 配置为上拉电阻器。 由于下拉电阻器的分压效应、最大上拉电平只能达到 2.9V。 然而、这已经满足后续级输入最低电平的要求。 这个问题是可以解决的。

此外、我咨询了我们的软件同事、发现此 IO 无法配置为推挽输出。 您能帮我检查一下它是否可以配置为推挽式吗? 如果是、则不会下拉此 IO 的高电平。

补充说明:此步骤确实是由 AM62A 引起的。 我已断开此 IO 连接的下游负载。

下图显示了此 IO 上电时的波形。

谢谢

Xiwen

您好、Liu Xiwen、

谢谢你。

AB20。 是 ETH_PHY_RESET

您似乎已将 100pF 电容器直接连接到悬空的 IO。 还有一个 10K 上拉电阻器。 存在下拉配置。

建议配置上拉或下拉电阻、以便在电源斜升期间使 EPHY 复位输入在复位状态下空洞。

如果需要、Yu 可以使用 22 pF 作为干扰滤波器以确保 EMC 稳健性。

此致、

Sreenivasa.

您好、Liu Xiwen、

[报价 userid=“626453" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1559214/am62a7-the-pins-generate-a-step-pattern-during-power-on/6049055 ]我想知道 在 AB20 IO 未连接到任何外设器件时如何生成该阶跃电压? 是由 SOC 内部的上拉电阻器引起还是由漏电流引起?IO 的最大漏电流为 10uA。 复位期间 SOC 上拉电阻器关闭。

在 IO 未端接的情况下、您可能会看到一些电压。

如果需要下拉 PHY 以保持复位状态、请不要安装接地电容器 (DNI)、并添加上拉电阻器、然后进行快速检查。 您可能看不到该步骤。

此致、

Sreenivasa.

您好、Sreenivasa

[引述 userid=“626453" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1559214/am62a7-the-pins-generate-a-step-pattern-during-power-on在测试 AM62A7 的引脚时、我们发现、在 AB20 上电(在 3V3 域中用作 GPIO)时、VCC3V3_SYS 将有大约 0.6V 的阶跃。 波形如下图。

抱歉、我之前的解释不正确。我衡量的是在 AM62A7 结束时接通电源的步骤。 此时、我断开了 SOC 和 PHY 之间的串联电阻 R1816。 电容器放置在串联电阻之后并靠近 PHY 端 因此、测量线上没有电容器。

谢谢、

Xiwen