主题中讨论的其他器件: TPS65224

工具/软件:

您好、工程师

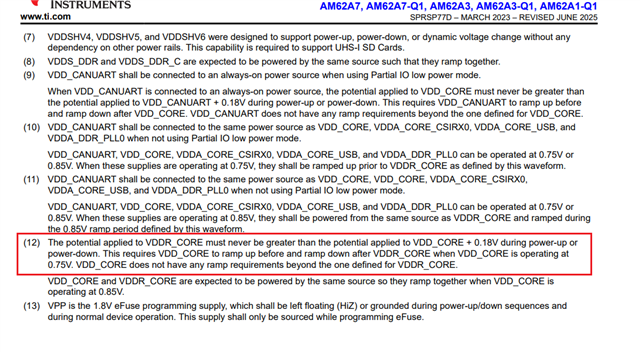

在测试 AM62A7 的断电序列时、我发现手册有这样的要求:VDDR_CORE (0V85) 在断电过程中需要始终小于 VDD_CORE (0V75)+ 0.18V。 也就是说、在断电过程中、我需要确保 VDDR_CORE 先断电、然后再关断 VDD_CORE。 或者、在整个断电过程中、VDDR_CORE 的断电速率应快于 VDD_CORE 的断电速率。 如果没有额外的放电电路、这非常困难、因为电源的断电时间与所连接电容器的电容值密切相关。

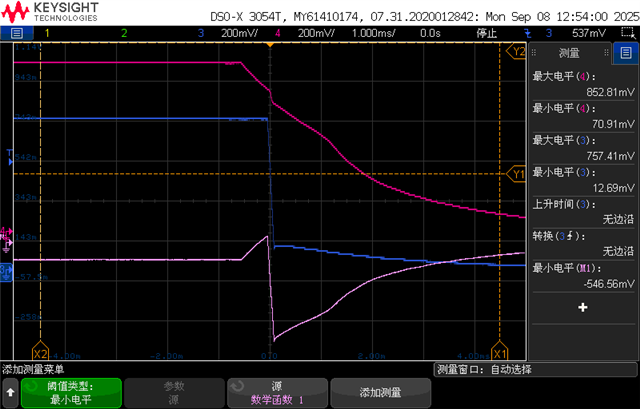

以下波形是我使用 PMIC TPS65224 传导的断电时序的实际测量值。 红线表示 VDDR_CORE、蓝线表示 VDD_CORE、紫线表示 VDD_CORE 和 VDDR_CORE 之间的差值。 此减值需要始终大于–0.18V。 从测试波形可以看出、这显然不符合要求;但是、可以确认、断电时序可以满足以下条件:先下拉 VDDR_CORE 的使能、然后下拉 VDD_CORE 的使能;VDD_CORE 由降压电路供电、而 VDDR_CORE 由 LDO 电路供电。 VDD_CORE 的断电速率非常快。

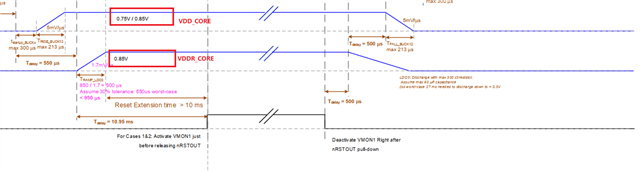

以下是 TPS65224 与 AM62A7 的 OTP 时序图。 可以看出、OTP 的断电时序也不符合 AM62A7 手册中规定的要求时序。

我的问题如下:

1、在通电阶段,很容易满足这一要求。 不过、在断电阶段、我想知道为什么 VDDR_CORE 需要比 VDD_CORE 完全断电、因为这两者实际上可以共享同一电源 0V85。

2.根据我目前的电源设计,这项要求无法满足。 它会对我的系统产生什么影响? 此时是否需要修改电路以满足时序要求?

感谢你的帮助。

Xiwen