Other Parts Discussed in Thread: AM62L, TMDS62LEVM, UNIFLASH

器件型号: AM62L

主题中讨论的其他器件: TMDS62LEVM、 UNIFLASH

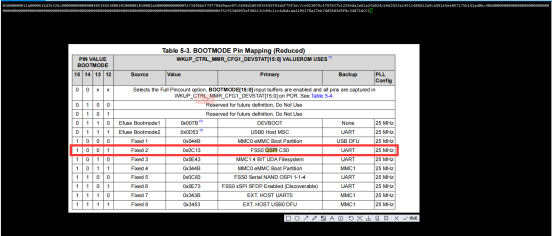

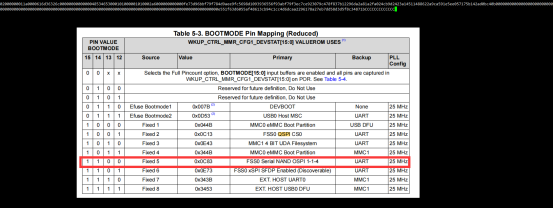

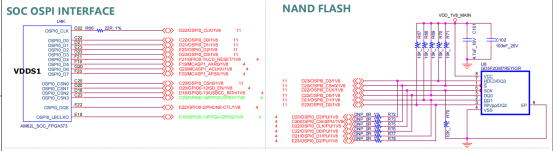

您好、专家。 目前、我们正在测试 AM62L32 的 QSPI 闪存启动。 下面是我们的原理图设计

无论是使用 FSS0 QSPI CS0 还是 FSS0 串行 NAND OSPI 1-1-4 模式、我们都无法正常引导。 特定的日志如下所示;但它可以正常读取和写入 QSPI 闪存。 我想问原因是什么?