Other Parts Discussed in Thread: SK-AM62A-LP

器件型号: AM62A7

主题中讨论的其他器件: SK-AM62A-LP

您好:

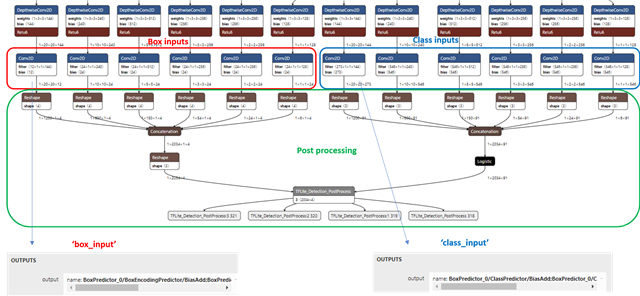

我正在尝试加速 A 面部标记/关键点检测模型 基础知识

SK-AM62A-LP 电路板。

该模型当前正在使用进行部署 SDK 10.01.04.00 和 TIDL 加速引擎 。

问题描述

- PC 验证: 该模型可在使用标准的 PC 上完美运行 .onnx 文件、生成准确稳定的关键点。

- AM62 部署: 在运行 TIDL 编译版本(使用原始版本 .onnx 和 AM62 上生成的工件文件夹)、预测的关键点是 错误 和 摇晃/抖动 帧到帧。

目标

我需要有关如何解决这两个问题的指导:

- 不准确的关键点: 从纯 ONNX 模型迁移到 TIDL 编译的工件时、预测偏移的最可能原因是什么?

- 抖动/抖动: 为什么 TIDL 推理会导致基于 PC 的 ONNX 推理中不存在的显著输出抖动?

有关为 AM62 修复地标模型或任何特定 TIDL 设置的任何提示都将非常有用。