Other Parts Discussed in Thread: SYSCONFIG

器件型号: AM6421

主题: SysConfig 中讨论的其他器件

您好:

我们正在尝试在与 phy ADIN1300 移植的客户电路板上运行 SDK 11.0.0.15 的 Enet CPSW 环回示例。 但它失败、输出如下。

tarting ARK MPU Bootloader ...

DMSC Firmware Version 11.0.7--v11.00.07 (Fancy Rat)

DMSC Firmware revision 0xb

DMSC ABI revision 4.0

INFO: Bootloader_runCpu:205: CPU r5f1-0 is initialized to 800000000 Hz !!!

INFO: Bootloader_runCpu:205: CPU m4f0-0 is initialized to 400000000 Hz !!!

INFO: Bootloader_runCpu:205: CPU a530-0 is initialized to 1000000000 Hz !!!

INFO: Bootloader_loadSelfCpu:257: CPU r5f0-0 is initialized to 800000000 Hz !!!

INFO: Bootloader_runSelfCpu:267: All done, reseting self ...

=============================

Enet Loopback: Iteration 1

=============================

CPSW_3G Test

Enabling clocks!

Mdio_open: MDIO Manual_Mode enabled

Open MAC port 1

EnetPhy_bindDriver: PHY 0: OUI:00a0ef Model:03 Ver:00 <-> 'ADIN1300' : OK

PHY 0 is alive

PHY 15 is alive

initQs() txFreePktInfoQ initialized with 16 pkts

Cpsw_handleLinkUp: Port 1: Link up: 100-Mbps Full-Duplex

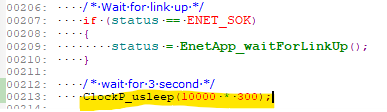

Assertion @ Line: 572 in C:/ti/flex_ti_am64x_sdk_11_00_00_15/source/networking/enet/core/examples/enet_loopback/enet_cpsw_loopback/loopback_test.c: EnetLpbk_verifyRxFrame(pktInfo, rxPktCnt) == true :经过调查后、它似乎需要在 loopback_test.c 中的 EnetApp_waitForLinkUp() 之后再等待 3 秒钟、然后它才能成功运行。

它需要再等待 3 秒的原因是、当处于 CPSW 的环回模式时、它不会检查寄存器 PHY_BMSR (01) 的 BMSR_LINKSTS(位 2)。 它只是返回 true、没有任何延迟或等待 SDK 代码 (cpsw.c 和 enetphy.c)。

对于 phy DP83867、没关系、因为如果它处于环回模式、寄存器 PHY_BMSR (01) 的 BMSR_LINKSTS(位 2)将始终为 0、并且不会影响数据接收。

对于 phy ADIN1300、它将不起作用、因为即使处于环回模式、它仍需要等待寄存器 PHY_BMSR (01) 的 BMSR_LINKSTS(位 2)变为 1、否则它将无法接收数据。 等待链路建立的时间约为 2.5 秒。

请提供此问题的解决方案。