器件型号: AM620-Q1

工具/软件:

您好、专家

这是该主题的扩展讨论、

问题:AM620-Q1:我们可以在 MCU LPM 下动态降低 MCU M4F PLL 的时钟速度吗

我们希望降低 MCUSS 工作时钟、以在 MCU LPM 下节省更多功率。

我们是否可以修改 MCUSS 工作时钟?

SDK:Linux 10.01.10.04

MCU SDK:10.01.00.33

谢谢您、

Gibbs

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

器件型号: AM620-Q1

工具/软件:

您好、专家

这是该主题的扩展讨论、

问题:AM620-Q1:我们可以在 MCU LPM 下动态降低 MCU M4F PLL 的时钟速度吗

我们希望降低 MCUSS 工作时钟、以在 MCU LPM 下节省更多功率。

我们是否可以修改 MCUSS 工作时钟?

SDK:Linux 10.01.10.04

MCU SDK:10.01.00.33

谢谢您、

Gibbs

嗨、Anil

感谢您的答复。

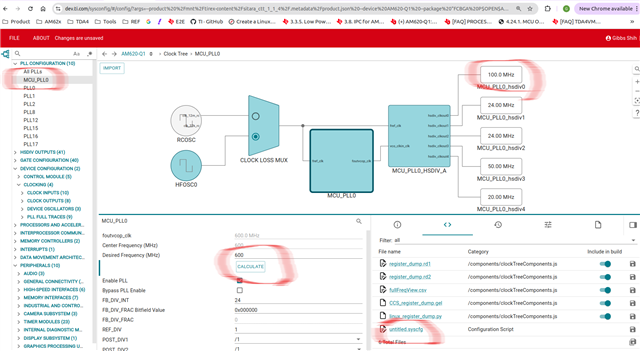

我尝试使用时钟树来配置 M4F 时钟、设置如下。

* unittled.syscfg

* Write custom configuration values to the imported modules. */ const PLL1 = system.clockTree["MCU_pllfracf2_ssmod_16fft0"]; PLL1.FB_DIV_INT_DivideValue = 24;

寄存器设置

我是否可以知道如何在 u-boot 或 Linux 代码中修改(更改)此设置?

谢谢你。

Gibbs

嗨、Nick

我们知道 在运行时不能更改频率、这是可以的。

我们希望 为具有静态设置的 M4 内核设置不同的频率、

M4F 内核频率是固定 200MHz 是我们的选择之一、因为我们想知道如何降低 M4 工作频率以降低功耗。

我知道需要在 M4 性能与功耗之间进行权衡、

我甚至使用 k3conf 来设置 M4 频率、但它不会改变。

因此、我们需要您帮助我们 在 Linux dts 或 u-boot 中为 M4 设置频率

谢谢你。

Gibbs

您好、Gibbs、

我懂了。

这种回答会有点模糊、因为我工作日的时间不够用。 如果明天需要更多信息、请告诉我。

这些说明假设 M4F 时钟设置与 PRU 时钟设置类似。

时钟树工具是了解您需要调整的时钟源的正确起点。 我建议上拉实际的 M4F 内核、而不是 PLL。 在左侧菜单中、转到“Processors and Accelerators > M4F“。

一旦您了解了要调整的时钟以及要将其设置为哪些频率、我希望我们使用 Linux 器件树文件中的“Clocks(时钟)“条目设置时钟频率。 我在快速搜索中看不到 M4F 的“时钟“条目、因此您可能需要添加它。

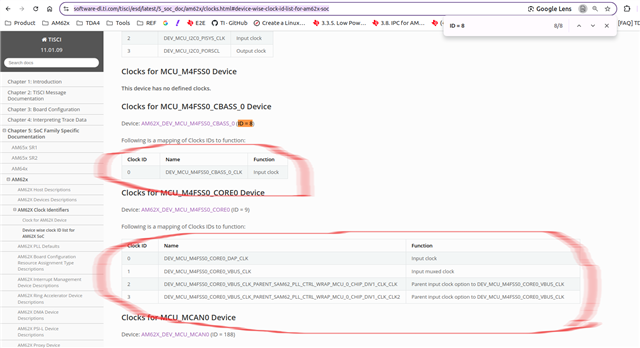

您可以在 TISCI 文档中找到每个时钟、PLL 输出等的时钟 ID、如下所示:

https://software-dl.ti.com/tisci/esd/latest/5_soc_doc/am62x/clocks.html

在我为 PRU 时钟编写的本文档中、您可以找到一些基本概念:

【常见问题解答】PRU_ICSSG:如何在 Linux 中查看和设置 PRU 内核频率?

此致、

Nick

您好、Nick、

感谢您的答复。

更新状态、进度并需要您的建议。

我已经完成了(研究)今天的两个案例。

案例 1:尝试直接修改寄存器设置而不修改 Linux DTS、并检查是否有 M4F 工作频率时钟变化。

案例 2:基于您的信息、并尝试在 Linux DTS 中添加节点属性

案例 1、步骤如下:

(1) 检查 MCU_M4FSS0*时钟

root@am62xx-lp-evm:~# k3conf dump clocks | grep EV_MCU_M4FSS0 | 8 | 0 | DEV_MCU_M4FSS0_CBASS_0_CLK | CLK_STATE_READY | 200000000 | | 9 | 0 | DEV_MCU_M4FSS0_CORE0_DAP_CLK | CLK_STATE_READY | 200000000 | | 9 | 1 | DEV_MCU_M4FSS0_CORE0_VBUS_CLK | CLK_STATE_READY | 400000000 | | 9 | 2 | DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARENT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK | CLK_STATE_READY | 400000000 | | 9 | 3 | DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARENT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK2 | CLK_STATE_READY | 200000000 |

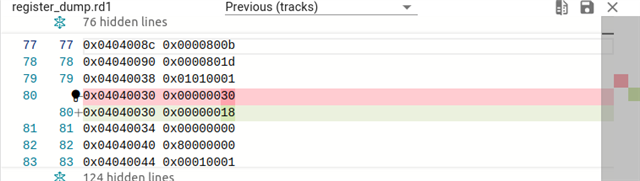

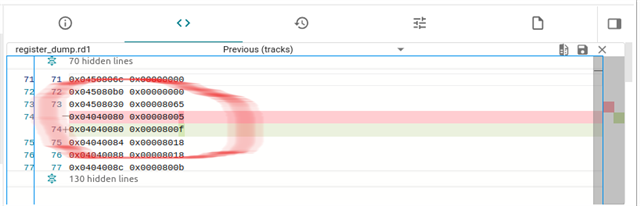

(2) 将时钟树中的 HSDIV 设置从 6 更改为 16、并生成寄存器设置集。

(3) 直接寄存器设置

root@am62xx-lp-evm:~# devmem2 0x04040080 /dev/mem opened. Memory mapped at address 0xffffb577d000. Read at address 0x04040080 (0xffffb577d080): 0x00008005 root@am62xx-lp-evm:~# devmem2 0x04040080 w 0x0000801f /dev/mem opened. Memory mapped at address 0xffff9291b000. Read at address 0x04040080 (0xffff9291b080): 0x00008005 Write at address 0x04040080 (0xffff9291b080): 0x0000801F, readback 0x0000801F root@am62xx-lp-evm:~# root@am62xx-lp-evm:~# devmem2 0x04040080 /dev/mem opened. Memory mapped at address 0xffff9f20a000. Read at address 0x04040080 (0xffff9f20a080): 0x0000801F

(4) 再次检查 MCU_M4FSS0*时钟、似乎需要努力

root@am62xx-lp-evm:~# k3conf dump clocks | grep EV_MCU_M4FSS0 | 8 | 0 | DEV_MCU_M4FSS0_CBASS_0_CLK | CLK_STATE_READY | 75000000 | | 9 | 0 | DEV_MCU_M4FSS0_CORE0_DAP_CLK | CLK_STATE_READY | 75000000 | | 9 | 1 | DEV_MCU_M4FSS0_CORE0_VBUS_CLK | CLK_STATE_READY | 150000000 | | 9 | 2 | DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARENT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK | CLK_STATE_READY | 150000000 | | 9 | 3 | DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARENT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK2 | CLK_STATE_READY | 75000000 |

问:我如何确保真正的努力来减少 M4SS 的运行时钟?

案例 2、步骤如下:

(1) 参考器件 ID 和时钟 ID 如下所示。

(2) 修改设备树。

k3-am62-mcu.dtsi

设备 ID 集 9、时钟 ID 集<9 1>、partent ID 集<9 2>

mcu_m4fss: m4fss@5000000 {

compatible = "ti,am64-m4fss";

reg = <0x00 0x5000000 0x00 0x30000>,

<0x00 0x5040000 0x00 0x10000>;

reg-names = "iram", "dram";

resets = <&k3_reset 9 1>;

/* Gibbs@202050828 */

clocks = <&k3_clks 9 1>;

assigned-clocks = <&k3_clks 9 1>;

assigned-clock-parents = <&k3_clks 9 2>;

assigned-clock-rates = <200000>;

firmware-name = "am62-mcu-m4f0_0-fw";

ti,sci = <&dmsc>;

ti,sci-dev-id = <9>;

ti,sci-proc-ids = <0x18 0xff>;

status = "disabled";

};

问题:

1. DTS 修改是否正确?

2.我感到非常困惑,如何将这些参数映射到 TRM(注册)? 因为我无法搜索正确的信息。

* DEV_MCU_M4FSS0_CBASS_0_CLK

* DEV_MCU_M4FSS0_CORE0_DAP_CLK

* DEV_MCU_M4FSS0_CORE0_VBUS_CLK

* DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARALT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK

* DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARALT_SK-AM62-PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK2

3.这是否只意味着在 Linux MCU DTS 中发生成功更改、然后它将出现在“kernel clk_summary “结果中?

非常感谢

Gibbs

您好、Nick

等待您的回复、更新一些困惑并询问我在最近几天发现了什么、因为我的客户还跟踪(+从中学习)该线程。

*如何为 M4F 内核映射时钟树和 k3config 转储结果?

root@am62xx-lp-evm:~# k3conf dump clocks | grep EV_MCU_M4FSS0 | 8 | 0 | DEV_MCU_M4FSS0_CBASS_0_CLK | CLK_STATE_READY | 200000000 | | 9 | 0 | DEV_MCU_M4FSS0_CORE0_DAP_CLK | CLK_STATE_READY | 200000000 | | 9 | 1 | DEV_MCU_M4FSS0_CORE0_VBUS_CLK | CLK_STATE_READY | 400000000 | | 9 | 2 | DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARENT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK | CLK_STATE_READY | 400000000 | | 9 | 3 | DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARENT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK2 | CLK_STATE_READY | 200000000 |

(1) DEV_MCU_M4FSS0_CBASS_0_CLK、参考

(2) DEV_MCU_M4FSS0_CORE0_VBUS_CLK、参考

(3) DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARALT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK (400MHz)

(4) DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARALT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK (200MHz)

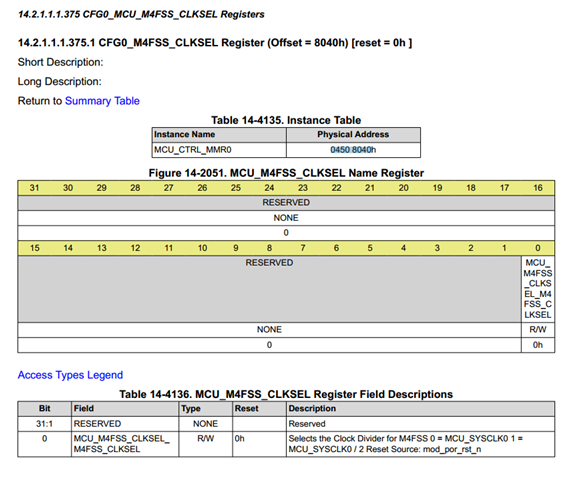

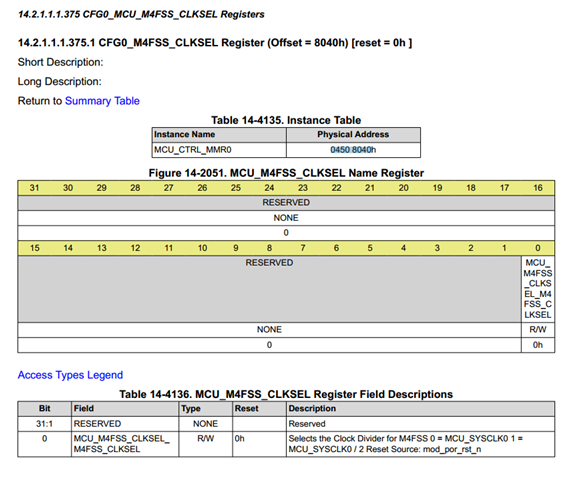

因此、“MCU_M4SS_CLKSEL"位于“位于寄存器“0x0450 8040“位 0 中进行选择。

因为“k3conf"仅“仅转储这些时钟设置、所以我认为我们可以“仅更改“用于 设置 MCU_M4FSS0_CORE0_VBUS_CLK_PARED_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK 的“DEV_MCU_M4F01_CORE0_VBUS_CLK_PARE_S 因此、 VBUS_CLOCK 应仅适用于 200MHz 或 400MHz。

如果要修改另一个时钟速率、必须通过设置 MCU_PLL0_HSDIV_A (0x04040080) 来手动修改“hsdiv_clockout0"</s>“

但我认为这应该有一些副作用、因为您也可以更改 DM R5 时钟设置等

*如何修改 Linux dts ?

(1) 更新 Linux 内核映像

(2) 更新 dtbo

ti-processor-sdk-linux-am62xx-evm-10.01.10.04/targetNFS/boot/dtb/ti$ sudo cp -f *.dtbo /media/gibbs/root/boot/dtb/ti/ ti-processor-sdk-linux-am62xx-evm-10.01.10.04/targetNFS/boot/dtb/ti$ sudo cp -f Image /media/gibbs/root/boot/

我认为我的设置应该正确、按如下所示进行更新。 但这并不奏效。

因为 DTS 设置正确后、它应该会出现在时钟树摘要 (/sys/kernel/debug/clk) 中

mcu_m4fss: m4fss@5000000 {

compatible = "ti,am64-m4fss";

reg = <0x00 0x5000000 0x00 0x30000>,

<0x00 0x5040000 0x00 0x10000>;

reg-names = "iram", "dram";

resets = <&k3_reset 9 1>;

/* Gibbs@20250828 */

clocks = <&k3_clks 9 1>;

assigned-clocks = <&k3_clks 9 1>;

assigned-clock-parents = <&k3_clks 9 2>;

assigned-clock-rates = <200000000>;

firmware-name = "am62-mcu-m4f0_0-fw";

ti,sci = <&dmsc>;

ti,sci-dev-id = <9>;

ti,sci-proc-ids = <0x18 0xff>;

status = "disabled";

};

*是否可以直接修改 Remoteproc 驱动器 (ti_k3_m4_remoteproc.c) 的寄存器设置?

我不确定这是一个好主意,我们可以使用“roremap ()“来直接“硬代码“设置寄存器没有 Linux dts ?

是否有示例代码?

需要您的 建议吗?

非常感谢

Gibbs

您好、Nick

等待您的回复、更新一些困惑并询问我在最近几天发现了什么、因为我的客户还跟踪(+从中学习)该线程。

*如何为 M4F 内核映射时钟树和 k3config 转储结果?

root@am62xx-lp-evm:~# k3conf dump clocks | grep EV_MCU_M4FSS0 | 8 | 0 | DEV_MCU_M4FSS0_CBASS_0_CLK | CLK_STATE_READY | 200000000 | | 9 | 0 | DEV_MCU_M4FSS0_CORE0_DAP_CLK | CLK_STATE_READY | 200000000 | | 9 | 1 | DEV_MCU_M4FSS0_CORE0_VBUS_CLK | CLK_STATE_READY | 400000000 | | 9 | 2 | DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARENT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK | CLK_STATE_READY | 400000000 | | 9 | 3 | DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARENT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK2 | CLK_STATE_READY | 200000000 |

(1) DEV_MCU_M4FSS0_CBASS_0_CLK、参考

(2) DEV_MCU_M4FSS0_CORE0_VBUS_CLK、参考

(3) DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARALT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK (400MHz)

(4) DEV_MCU_M4FSS0_CORE0_VBUS_CLK_PARALT_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK (200MHz)

因此、“MCU_M4SS_CLKSEL"位于“位于寄存器“0x0450 8040“位 0 中进行选择。

因为“k3conf"仅“仅转储这些时钟设置、所以我认为我们可以“仅更改“用于 设置 MCU_M4FSS0_CORE0_VBUS_CLK_PARED_SAM62_PLL_CTRL_WRAP_MCU_0_CHIP_DIV1_CLK_CLK 的“DEV_MCU_M4F01_CORE0_VBUS_CLK_PARE_S 因此、 VBUS_CLOCK 应仅适用于 200MHz 或 400MHz。

如果要修改另一个时钟速率、必须通过设置 MCU_PLL0_HSDIV_A (0x04040080) 来手动修改“hsdiv_clockout0"</s>“

但我认为这应该有一些副作用、因为您也可以更改 DM R5 时钟设置等

*如何修改 Linux dts ?

(1) 更新 Linux 内核映像

(2) 更新 dtbo

ti-processor-sdk-linux-am62xx-evm-10.01.10.04/targetNFS/boot/dtb/ti$ sudo cp -f * /media/gibbs/root/boot/dtb/ti/ ti-processor-sdk-linux-am62xx-evm-10.01.10.04/targetNFS/boot$ sudo cp -f Image /media/gibbs/root/boot/

我认为我的设置应该正确、按如下所示进行更新。 但这并不奏效。

因为 DTS 设置正确后、它应该会出现在时钟树摘要 (/sys/kernel/debug/clk) 中

mcu_m4fss: m4fss@5000000 {

compatible = "ti,am64-m4fss";

reg = <0x00 0x5000000 0x00 0x30000>,

<0x00 0x5040000 0x00 0x10000>;

reg-names = "iram", "dram";

resets = <&k3_reset 9 1>;

/* Gibbs@20250828 */

clocks = <&k3_clks 9 1>;

assigned-clocks = <&k3_clks 9 1>;

assigned-clock-parents = <&k3_clks 9 2>;

assigned-clock-rates = <200000000>;

firmware-name = "am62-mcu-m4f0_0-fw";

ti,sci = <&dmsc>;

ti,sci-dev-id = <9>;

ti,sci-proc-ids = <0x18 0xff>;

status = "disabled";

};

*是否可以直接修改 Remoteproc 驱动器 (ti_k3_m4_remoteproc.c) 的寄存器设置?

我不确定这是一个好主意,我们可以使用“roremap ()“来直接“硬代码“设置寄存器没有 Linux dts ?

是否有示例代码?

需要您的 建议吗?

非常感谢

Gibbs

您好、Nick

更新状态。

我认为 M4FSS0_CORE0_VBUS_CLK 的 Linux DTS 设置已经很有问题、因为我可以在“时钟树摘要“中看到它

clk:9:3 0 0 0 200000000 0 0 50000 Y deviceless no_connection_id

clk:9:2 0 0 0 400000000 0 0 50000 Y deviceless no_connection_id

clk:9:1 0 0 0 400000000 0 0 50000 Y deviceless no_connection_id

epwm_tbclk2 0 0 0 0 0 0 50000 N deviceless no_connection_id

epwm_tbclk1 0 0 0 0 0 0 50000 N deviceless no_connection_id

epwm_tbclk0 0 0 0 0 0 0 50000 N deviceless no_connection_id

clk-0 0 0 0 12288000 0 0 50000 Y deviceless no_connection_id

但即使我更改了“assigned-clock-partments =<&K3_CLKS 9 2>“或“ assigned-clock-partments =<&K3_CLKS 9 3>“ 、M4FSS0_CORE0_VBUS_CLK 也始终保持 400MHz、它在 DTS 中是否具有任何错误的设置? 请给我们任何建议。

/* Gibbs@20250828 */ clocks = <&k3_clks 9 1>; assigned-clocks = <&k3_clks 9 1>; assigned-clock-parents = <&k3_clks 9 3>; assigned-clock-rates = <200000000>;

/* Gibbs@20250828 */ clocks = <&k3_clks 9 1>; assigned-clocks = <&k3_clks 9 1>; assigned-clock-parents = <&k3_clks 9 2>; assigned-clock-rates = <200000000>;

谢谢你。

Gibbs

您好、Gibbs、

谢谢你的耐心,以及你坚持对我的 ping。

抬头看,我最近在家里去世了,所以我将在星期五&星期一办公室以外。 今天我花了一些时间查看您的主题、我会在离开之前再次在星期四上做出回复。

我们是否正在查看合适的时钟?

是的。

https://software-dl.ti.com/tisci/esd/latest/5_soc_doc/am62x/clocks.html#device-wise-clock-id-list-for-am62x-soc 仅列出 2 个输入时钟:DAP 时钟和 VBUS 时钟。 DAP 时钟仅用于调试和跟踪。 因此、我们应查看 VBUS_CLK 输入。

我预计这 2 个输入时钟是从 MCU_SYSCLK0 输入到 MCU_M4FSS_CLKSEL。 因此、我们应该允许在频率 MCU_PLL0_HSDIV_A_clkout0(默认为 400MHz) 和)和 MCU_PLL0_HSDIV_A_clkout0/2 之间进行选择。

仔细检查、此时 200MHz 与客户是否正常?

如果是这样、我们可以非常轻松地为 MCU_M4FSS_CLKSEL 选择另一个输入(应该是)。

查看 Linux 器件树文件设置

无需在此处设置频率。 我们应该可以选择输入时钟。

我希望它看起来像这样(今天没有时间进行测试):

clocks = <&k3_clks 9 2>, <&k3_clks 9 3>; assigned-clocks = <&k3_clks 9 1>; assigned-clock-parents = <&k3_clks 9 3>;

现在、交换分配的时钟父级是否会改变 M4F 内核的频率?

此致、

Nick

嗨、Nick

遵循您的评论。

我认为测试结果是 samem、频率不变。

/* Gibbs@20250828 */ clocks = <&k3_clks 9 2>, <&k3_clks 9 3>; assigned-clocks = <&k3_clks 9 1>; assigned-clock-parents = <&k3_clks 9 3>; assigned-clock-rates = <100000000>;

谢谢你。

Gibbs

嗨、Gibbs、

根据我能说的、M4F Remoteproc 驱动程序无法根据器件树参数控制时钟。 因此、添加分配到的时钟可能不起作用。

例如、GPU 能够执行以下操作:

您能否尝试更新 board_init_f 函数中的 MCU M4F 时钟分频器寄存器?

这应该在 R5 SPL 级进行。 您可以使用'writel'在末尾添加一行来写入寄存器。 所以它将是'writel(

、 )'Anshu

您好、 Anshu Madwesh

对不起,我现在有时间测试.

基本上、它通过在 u-boot 源代码中进行硬编码来工作。

void board_init_f(ulong dummy)

{

struct udevice *dev;

int ret;

if (IS_ENABLED(CONFIG_CPU_V7R)) {

setup_k3_mpu_regions();

rtc_erratumi2327_init();

}

/*

* Cannot delay this further as there is a chance that

* K3_BOOT_PARAM_TABLE_INDEX can be over written by SPL MALLOC section.

*/

store_boot_info_from_rom();

ctrl_mmr_unlock();

//Gibbs@20250426

writel(0x0000801f, 0x04040080);

/* Init DM early */

spl_early_init();

wkup_ctrl_remove_can_io_isolation_if_set();

我认为我们需要再次进行测试、以检查降低 MCU 时钟速度时的任何副作用。

谢谢你。

Gibbs