Other Parts Discussed in Thread: SYSCONFIG, SK-AM62A-LP

器件型号: AM62A7

主题中讨论的其他器件: SysConfig、 SK-AM62A-LP

尊敬的专家:

问:我的理解是否正确、AM62A 的主域 (A53) 可以控制 MCU 域 (R5F) 的外设?

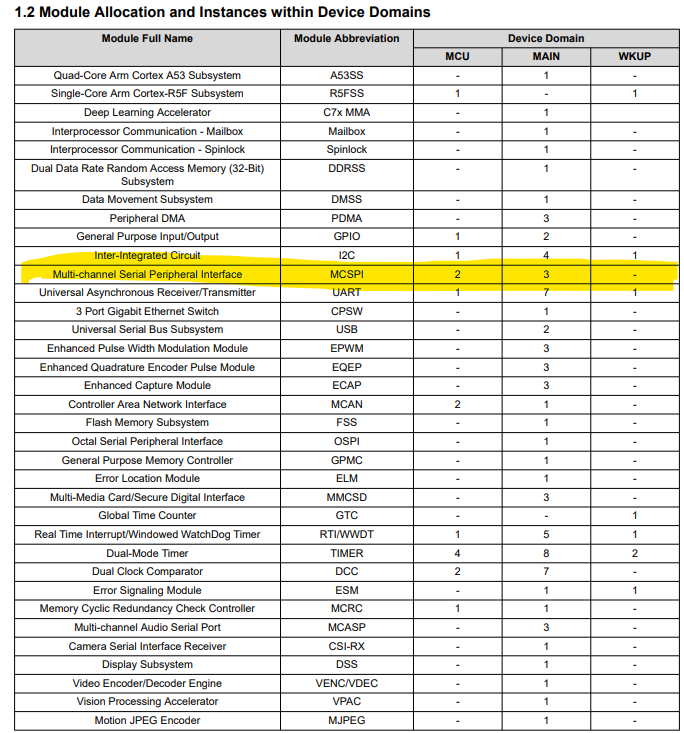

具体来说、主域 (A53) 总共可以控制 5 个 SPI 接口(包含 3 个主 SPI 和 2 个 MCU SPI)是否正确?

我从以下 URL 了解到、MCU 域可以控制主域的一些外设。

AM62Ax MCU+ SDK:从 MCU 域访问主域和唤醒域外设

在 MCU+SDK v11.1 中、我确认了通过导入“mcspi_loopback_am62ax-sk_a53ss0-0_nortos_gcc-AArch64"并“并在 SysConfig 中对其进行配置、可以进行编译。

根据 TRM 的“3.3 发起方/目标连接“部分、我了解它们是内部连接的。

此致、

正常