Other Parts Discussed in Thread: SYSCONFIG

器件型号: TDA4VH-Q1

主题: SysConfig 中讨论的其他器件

尊敬的 TI 团队:

SDK - 11.

引导序列 — SPL

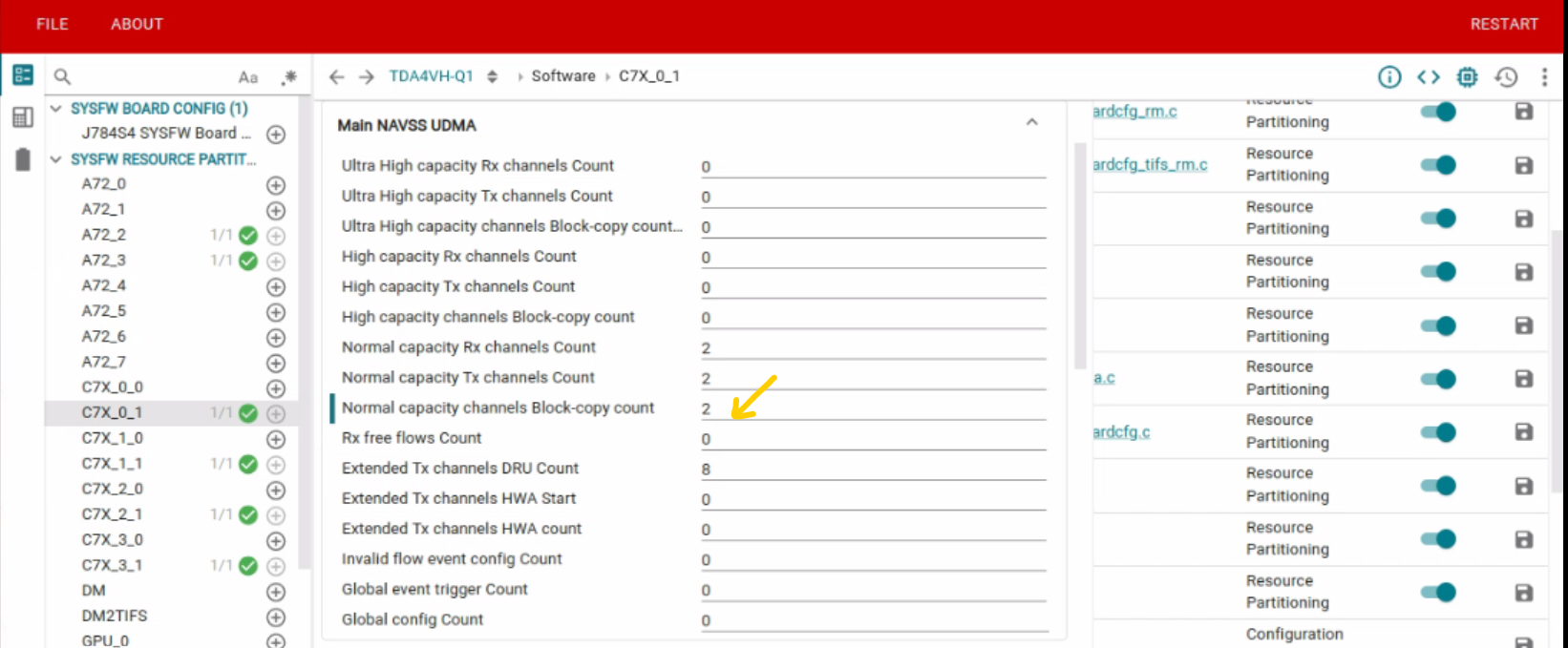

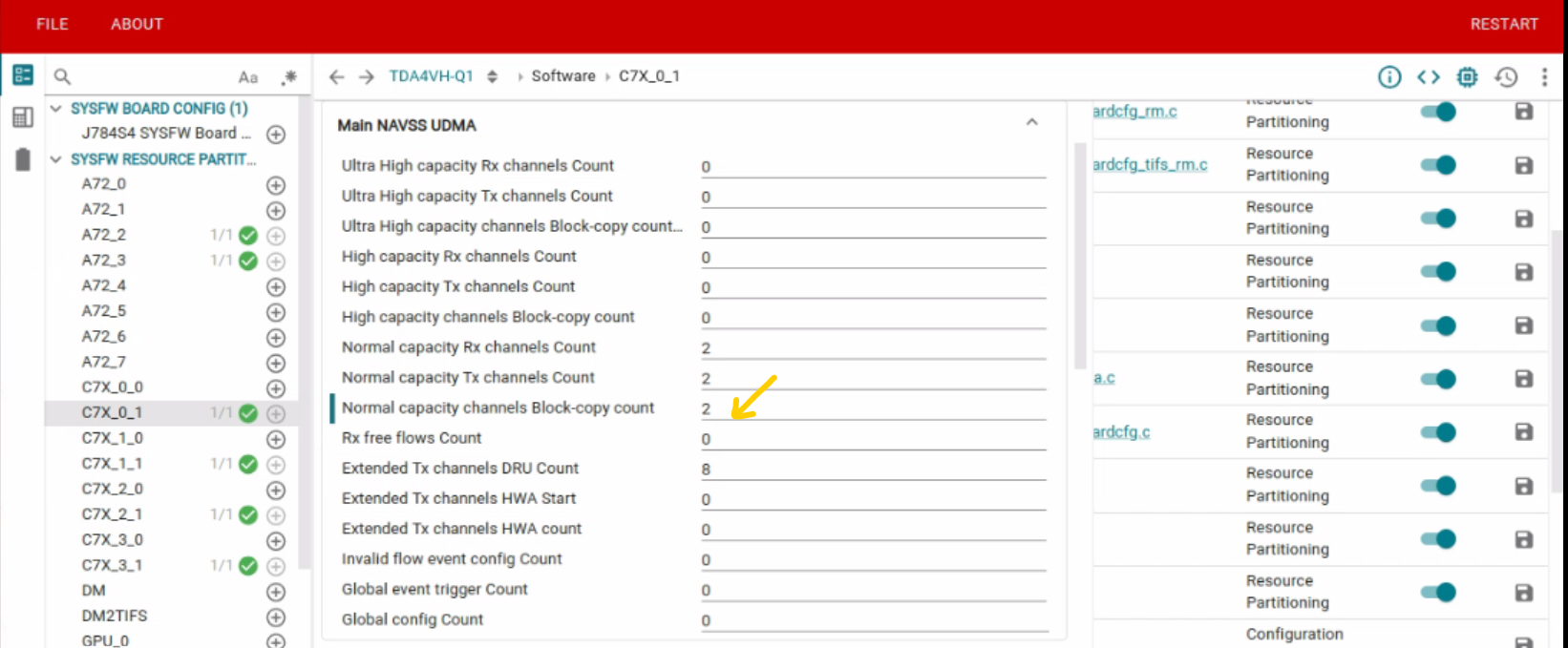

我尝试使用 SysConfig 工具增加块复制的通道数、并使用 Linux SDK 中的顶级 make 文件生成 u-boot

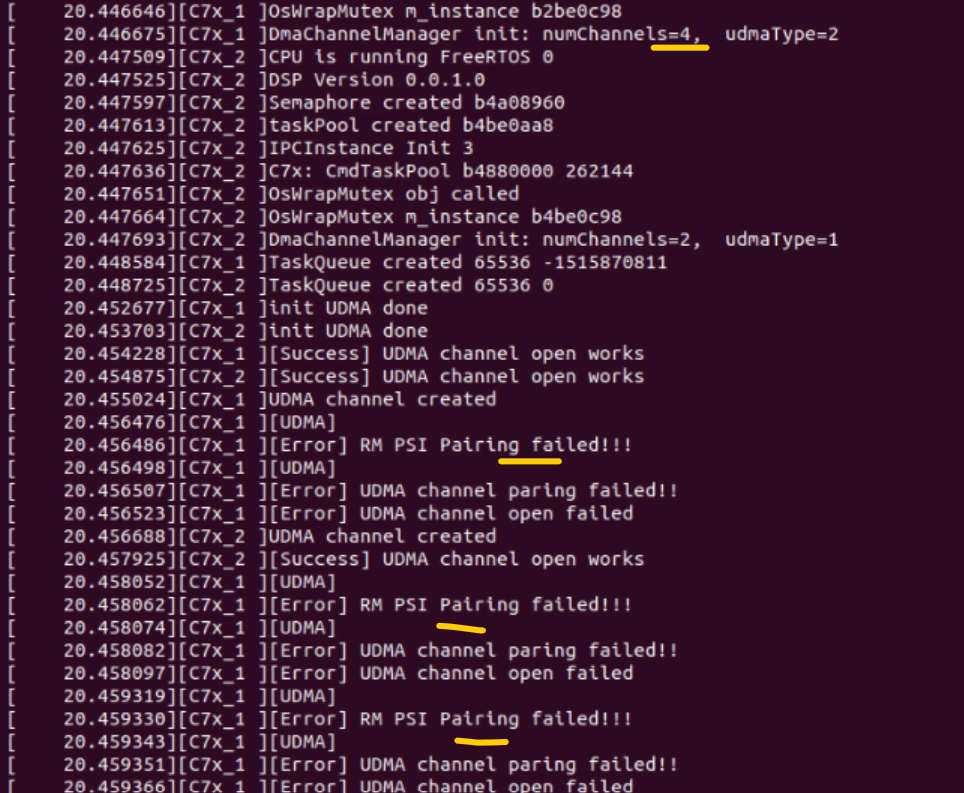

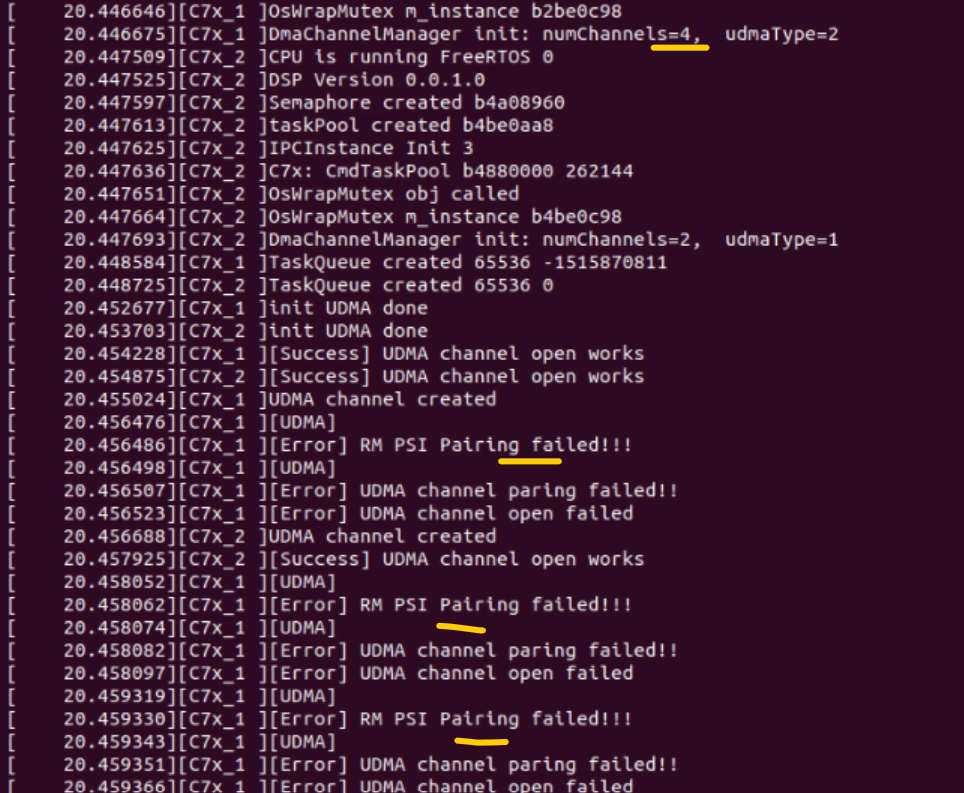

我在 c7x 中遇到错误

解决这个问题的方法

谢谢

此致

Gowtham

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: SYSCONFIG

器件型号: TDA4VH-Q1

主题: SysConfig 中讨论的其他器件

尊敬的 TI 团队:

SDK - 11.

引导序列 — SPL

我尝试使用 SysConfig 工具增加块复制的通道数、并使用 Linux SDK 中的顶级 make 文件生成 u-boot

我在 c7x 中遇到错误

解决这个问题的方法

谢谢

此致

Gowtham

它看起来像 Udma_chPair功能出现故障。 我假设您从中删除了一个信道 C7x1 相位滞后。

此外、为什么需要增加块复制通道?

我的固件运行在上面 C7x_2 和 C7x_3 、它还将 DRU 通道用于 DMA。

我们已按如下方式配置 DRU 通道:

C7x_0–8、C7x_1–8、C7x_2–6 和 C7x_3–4 。

以下是我们的 DMA DRU 通道配置。 引导模式 CORE_0 和 CORE_1 、我们的 DMA 崩溃 C7x_2 和 C7x_3 。

我的问题是:TIDL 何时运行 C7x_0 和 C7x_1 、它仅使用 16 个 DMA DRU 通道。 这是否会影响分配给的 10 个 DMA DRU 通道 C7x_2 和 C7x_3 ?

您好、

我们已按如下方式配置了 DRU 通道:

C7x_0–8、C7x_1–8、C7x_2–6 和 C7x_3–4 。

以下是我们的 DMA DRU 通道配置。 引导模式 CORE_0 和 CORE_1 、我们的 DMA 崩溃 C7x_2 和 C7x_3 .

您是否 也对环形加速器计数进行了修改?

我的问题是:TIDL 在上运行时 C7x_0 和 C7x_1 、它仅使用 16 个 DMA DRU 通道。 这是否会影响分配给的 10 个 DMA DRU 通道 C7x_2 和 C7x_3 ?

因为它们使用不同的通道、所以不

此致、

Sivadeep

您好、

对迟来的答复表示歉意。 问题仍然存在吗?

如果 TIDL 运行会在我的最后两个内核中使用 DRU 通道来影响我的 DMA、请考虑将数据从 DDR 复制到 L2。 [/报价]目前正在研究如何使用 TIDL DRU 和 c7x_2 和 c7x_3 中的其他 DRU 通道、但我认为您正在为 c7x_2 和 c7x_3 使用非 DRU 通道、这不会导致任何问题。

此致、

Sivadeep