Other Parts Discussed in Thread: AM4372

部件号: AM4372

TI 团队大家好、

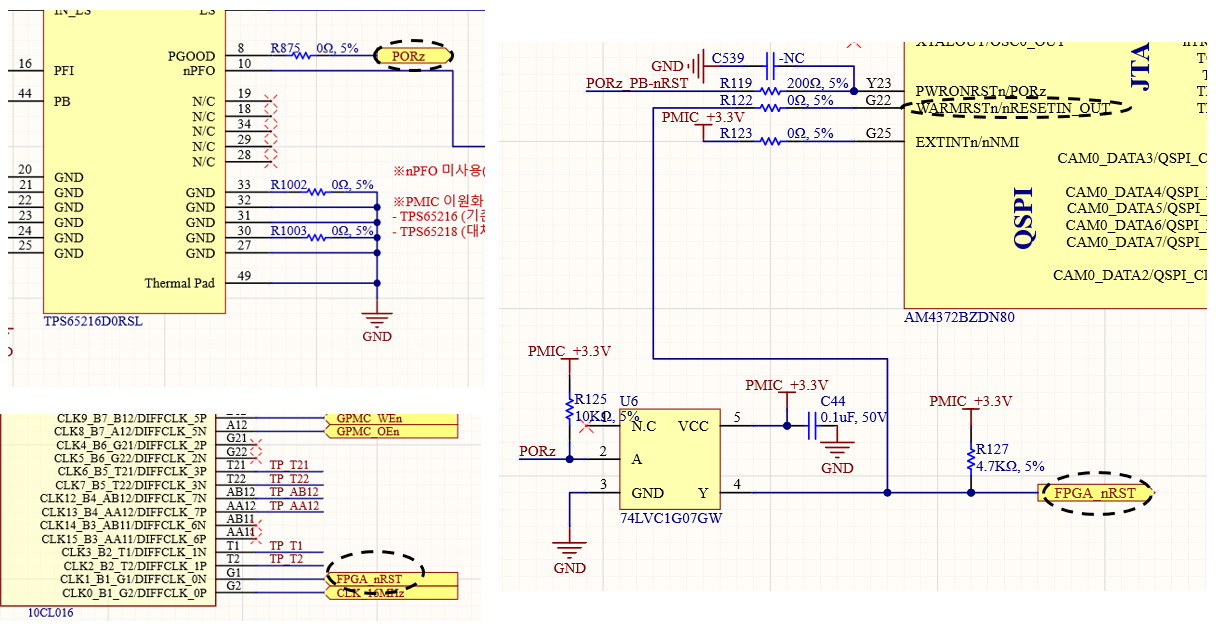

我们在 BRM100 主板上使用 AM4372 CPU、结构如下:

AM4372 (CPU、TI)–PMIC (TPS65216D0RSL)–FPGA (10CL016、Altera) 。

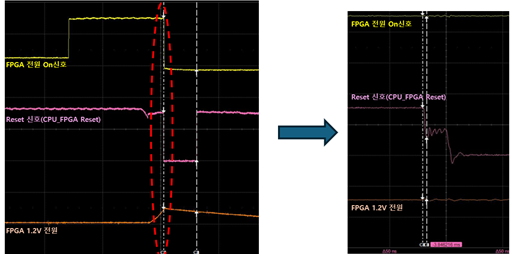

我们观察到在开机期间现场出现间歇性引导故障。 CPU 完成引导后、上出现噪音 WARMRSTn 引脚 (G22) 、它连接到 FPGA 复位网络。 此噪声似乎会意外触发 CPU 的热复位。

我们的理解是 WARMRSTn 引脚的运行方式 功率斜升期间的输入 然后变为 POR 和启动完成后输出 。 但是、即使在引脚配置为输出后、我们也会看到热复位事件、这会令人困惑。

问题:

- 我们对 WARMRSTn 引脚行为(斜升期间的输入,引导后的输出)的理解是否正确?

- 如果引脚处于输出模式、为什么此网络上的噪声会导致启动后的热复位?

- 是否有任何推荐的方法 在启动期间禁用热复位输入功能、并在系统稳定后重新启用热复位输入功能 ? 如果是、我们应该使用哪个 MMR 寄存器?

- 是否有关于的任何 TI 指南或最佳实践 CPU 和 FPGA 之间的共享复位网 避免此类问题? 例如、RC 滤波或施密特触发缓冲。

附件为:

- 显示 WARMRSTn 连接的原理图片段。

- 显示 FPGA 功率斜升期间噪声的示波器波形。

任何澄清或设计建议都将不胜感激。

感谢您的支持。

此致、

插孔