This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

1、修改 DDR ATYPE 值、默认值为0、使用 R5F 和 C66设置 ATYPE 3。

如所述、当设置 ATYPE=3时、当 A72与 C66通信时、A72需要手动使其一致。

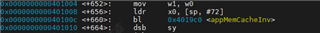

所以、在 A72代码中、我们调用了 appMemCacheWb (也称为 DSB、内存边界)、然后进行数据发送。 当 C66收到时、称为 appMemCacheWbInv。

但是、我们发现数据不正确、有些数据是错误的。 当我们设置 ATYPE=0时、数据不会出错。

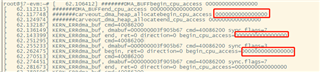

然后、查看 appMemCacheWb 、并在 Linux 内核代码的驱动程序 dma-buf 中添加打印信息。

但我们发现未调用高速缓存相关函数、且 calllbak 函数为 NULL

现在、我们不是如何处理这个问题的、而是给我们一些建议、谢谢。