This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

各位专家、您好!

我正在尝试了解 SDL 软件包中 DCC 的默认代码,该文件夹为:SDL_1.0/SDL_RLS_01.00.00/ SDL/examples/DCC/UC8。

源时钟是 RC OSC、测试时钟是 HFOSC0、我也可以理解 HFOSC0是19200 (19.2MHZ)、但 RC OSC 时钟是什么? 我在代码中看到的是333334,但我只能在 TRM 中看到它的频率为12.5MHz,您能不能指导我们这是什么,它与硬件是否相关?

此外、我们为什么选择该时钟333334作为输入、它是否由硬件连接确定?

提前感谢。

BR、

新生儿

您好、Neo、

根据安全手册、DCC 是一种诊断机制、可用于检测时钟问题、包括不正确的频率和时钟源之间的漂移。 DCC 使用另一个输入时钟作为基准来测量可选时钟源的频率。 可通过软件选择基准时钟和被测时钟、时钟频率的预期比率也是如此。

对于 UC8、代码看起来有问题、 我在内部进行跟踪。

UC8的代码

根据 TRM、并将变量命名与下表匹配、随后用户将需要使用以下设置:

其频率为:

并与 UC8代码中的注释保持一致、其中

不匹配的是:

那么测试案例是如何通过的?

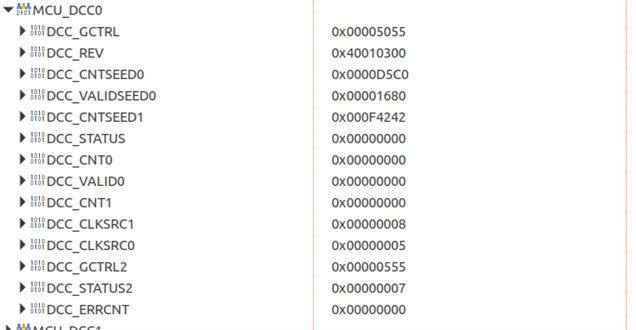

运行 UC8时、可以 看到 MCU_DCC0的 CLKSRC 设置如下。

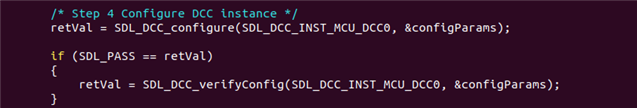

与步骤4中的代码匹配、其中正在配置 MCU_DCC0。

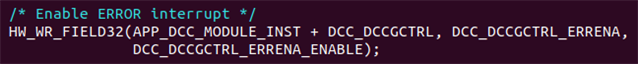

在配置 MCU_DCC0后、启用 MCU_DCC2中断

由于 MCU_DCC0 在分配的时间段内运行并通过、因为没有中断关闭。

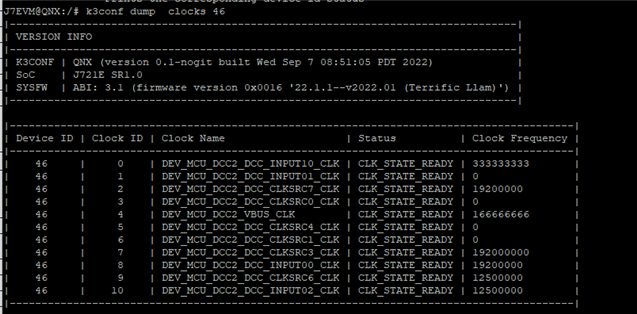

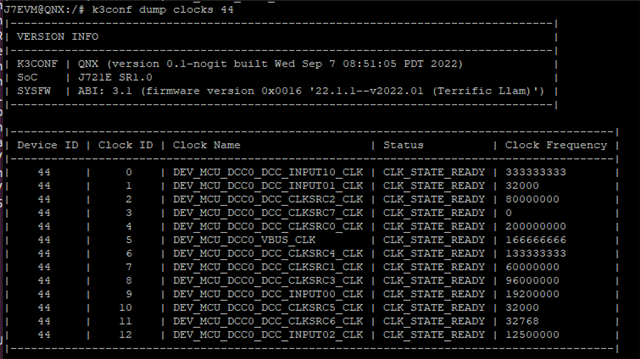

下面是通过 A72的 k3conf 查看 MCU_DCC2和 MCU_DCC0时钟的样子。

此致、

基普

您好、Neo、

我的理解是、 已经为您提供了一个解决此问题的补丁、[PROC_SDS-3701] DCC 中涵盖了该补丁:用于选择除 clock0_0之外的 Input0时钟的值不正确-德州仪器(TI) JIRA。

关闭此主题。

此致、

基普