您好:

我们有一个在 Linux 上运行的定制板、它在地址和数据多路复用模式下将 FPGA 连接到 GPMC。似乎我们可以成功写入 FPGA、但只能从 FPGA 读取0x0。

下面是我们的 DTS 文件:

SRAM_X16_DEFAULT:SRAM_X16_DEFAULT{ pinctrl-single、PIN=< AM33XX_IOPAD (0x800、(PIN_INPUT_PULLUP | MUX_MODE0))/* GPMC_AD0*/ AM33XX_INPULLUG_AD0*/AM33MC_AD0*/AM33MC_ADPULLUG_AD0*/AM33MC_AD0*/AM33MC_AD_AD0*/AM33MC_ADPULLUPULLUP (0x804*/AM33MC_AD_AD0*/AM33MC_AD_AD_AD_AD0*/AM33MC_AD0*/AM33MC_AD0*/AM33MC_AD_AD0_AD_AD_PUV_AD0*/AM33MC_AD0*/AM33MC_AD_PUV_AD_AD0*/AM33MC_AD0_AD_AD_PIN_AD0*/AM33MC_AD_AD_AD0*/AM33MC_PIN_AD_ (PIN_INPUT_PULLUP | MUX_MODE0))/* GPMC_AD7.GPMC_AD7*/ AM33XX_IOPAD (0x820、(PIN_INPUT_PULLUP | MUX_MODE0)/* GPMC_AD8_AD8* (0x824_GPIO_PULLUP)/AM339_MODE_IN_MODE8*(0x8_AM_MODE_IN_AD0*(0x824_AM_AM_MODE_MODE_IN_MODE8_AM_AM_MODE8)/PIN_MODE_MODE_AD0*(0x83*) (PIN_INPUT_PULLUP | MUX_MODE0))/* GPMC_AD15.GPMC_AD15*/ AM33XX_IOPAD (0x870、(PIN_INPUT_PULLUP | MUX_MODE0))/* GPMC_wait0.GPMC_wait0*/ AM33XX_IOPAD (0x874、(MUX_MODE0)|输出引脚 /* GPMC_WPN */ AM33XX_IOPAD (0x87c、(PIN_OUTPUT | MUX_MODE0)) /* GPMC_csn0.GPMC_csn0 */ AM33XX_IOPAD (0x884、(PIN_OUTPUT | MUX_MODE0)) /* GPMC_csn2.GPMC_csn2 */ AM33XX_IOPAD (0x88c、(PIN_OUTPUT | MUX_MODE0)) /* GPMC_clk */ AM33XX_IOPAD (0x890、(PIN_OUTPUT | MUX_MODE0))/* GPMC_advn_ALe.GPMC_advn_ALE */ AM33XX_IOPAD (0x894、(PIN_OUTPUT | MUX_MODE0))/* GPMC_adv_AL_AL_REN * *(0xMC_IN_IN_IN_IN_OUTP_0_0*)*(0xMC_MODIV_0_IN_MR_0_MODIO898x *)*(PIN_IN_IN_IN_MODIO0_IN_IN_IN_EN_IN_IN_IN_IN_IN_IN_EN_MODIO894*)

&GPMC{ status ="确定"; pinctrl-names ="默认值"; pinctrl-0 =<&SRAM_X16_default>; 范围=<0 0x08000000 0x01000000>; FPGA@0、0{ compatible ="MTD-ram"; reg =<0 0x1000000>;// CS0、base_address、size of NOR bank-width =<2>;// 16位 GPMC、device-width =<2>;// 16位 GPMC、mux-add-data =<2>;//地址数据多路复用 // GPIMC_cs =<2ns;//相应的 GPMC_CLMC_s = GPMC_ns-ns; //从开始周期开始的有效时间 GPMC、cs-rd-off-ns =<186>;//从开始周期开始的时间开始的无效时间读访问 GPMC、cs-wr-off-ns =<186>;//从开始周期开始的失效时间开始写入访问// ADV 信号时序( 与 GPMC_FCLK 相对应的 ADC_ADV)= GPIOn GPMC_3ns; //从开始周期开始的有效时间 GPMC、Adv-rd-Off-ns =<48>;//从开始周期开始的时间开始的无效时间读访问 GPMC、adv-wr-off-ns =<48>;//从开始周期开始的失效时间开始写入访问 // OE 信号时序(对应于 GPMC_FCLK 的 GPMC_CONK) = 54ns; //从开始周期开始的有效时间 GPMC、OE-OFF-ns =<168>;//从开始周期开始的失效时间 // WE 信号时序(GPMC_FCLK 的 num)对应于 GPMC_CONFIG4 GPMC、WE-ON-ns =<54>;//从开始周期开始的有效时间 GPMC、WE-OFF-ns = 168ns; //从开始周期时间开始失效的时间 //与 GPMC_CONFIG5 GPMC 对应的访问时间和周期时间计时(GPMC_FCLK 的数量),第-cycle-ns =<186>;//开始周期时间和第一个数据有效 GPMC 之间的延迟,电源周期-ns =<186>;//总写入周期时间 GPMC,<114-ns = GPMC<114>; GPMC-ns =<114-ns;GPMC-ns =<114-ns //多个访问中连续字之间的延迟 //访问时间和周期时间时序(GPMC_FCLK 的数量)对应于 GPMC_CONFIG6 GPMC、总线翻转-ns =<12>; //两次连续访问之间的总线周转延迟 //到同一芯片选择(读取到写入)或不同 //芯片选择(读取到读取到写入) GPMC、cycle2cycle-delay-ns =<18>;//芯片选择两次连续访问之间的高脉冲延迟 GPMC、wr-data-mux-bus-ns =<90>; //确定 在哪个 GPMC.FCLK 上升沿上、//同步突发写入的第一个数据在添加/数据多路复用总线中被驱动。 GPMC、wr-access-ns =<186>;//从 StartAccessTime 到相应的 GPMC.FCLK 上升沿的延迟 //连接的存储器用于首次数据采集的 GPMC.CLK 上升沿。 GPMC、cycle2cycle-samecsen;//在对同一芯片选择(任何访问类型)的两次连续访问之间添加 Cyclle2CyclleDelay ;GPMC、cycle2cycle-diffcsen;//在对不同芯片选择(任何访问类型)的两次连续访问之间添加 Cyclle2CyclleDelay GPMC、等待读取="false"; GPMC、写入等待="false"; GPMC、SYNC-READ ="真"; GPMC、SYNC-WRITE ="真"; #address-cells =<1>; #size-cells =<1>; }; };

和 GPMC_CONFIG1~GPMC_CONFIG7寄存器的值为:

WRAPBURST:0

自述:0

准备时间:1.

WRITEMULTIPLE:0

WRITETYPE:1.

CLKACTIVATIONTIME:00

ATTACHDDEVICEPAGELNGTH:00

WAITREADMONITORING:0

WAITWRITEMONITORING:0

WAITMONITORINGTIME:00

WAITPINSELECT:00

设备大小:01

设备类型:00

MUXADDATA:10.

状态:0

GPMCFCLKDIVIDER:00

CSWROFFTIME:10011

CSRDOFFTIME:10011

CSEXTRADELAY:0

CSONTIME:0000

ADVAADMUXWROFFTIME:000

ADVAADMUXRDOFFTIME:000

ADVWROFFTIME:00101

ADVRDOFFTIME:00101

ADVEXTRADELAY:0

ADVAADMUXONTIME:000

ADVONTIME:0010

WEOFFTIME:10001

WEEXTRADELAY:0

WONTIME:0110

OEAADMUXOFFTIME:000

OEOFFTIME:10001

OEEXTRADELAY:0

OEAADMUXONTIME:000

OEONTIME:0110

PAGEBURSTACESSTIME:0001

RDACCESSTIME:01100

WRCYCLETIME:10011

RDCYCLETIME:10011

WRACCESSTIME:10011

WRDATAONADMUXBUS:1001

CYCLE2CYCLEDELAY:0010

CYCLE2CYCLESAMECSEN:1.

CYCLE2CYCLEDIFFCSEN:1.

BUSTURNAROUND:0010

MASKADDRESS:1111

CSVALID:1.

BASEADDRESS:001000

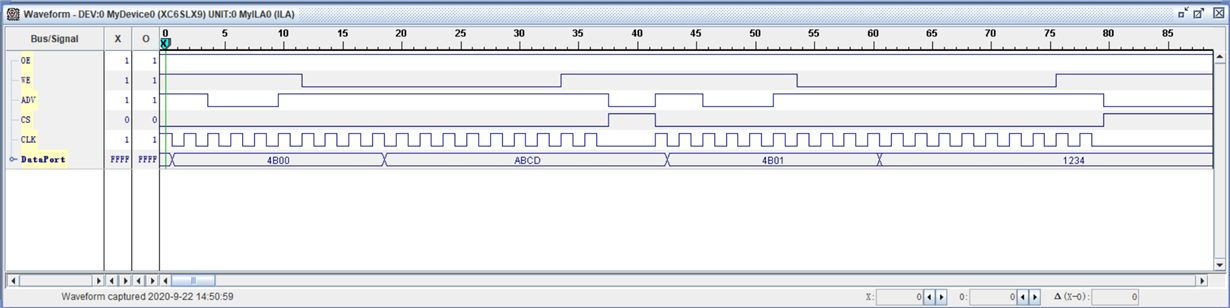

将0x1234abcd 写入0x8009600:

当我们阅读:

数据已放置在数据/地址行上。 但是、AM3358没有提供任何内容。

我们的硬件方案是:

我们希望有人能给我们一些建议。