主题中讨论的其他器件:AM5718

您好!

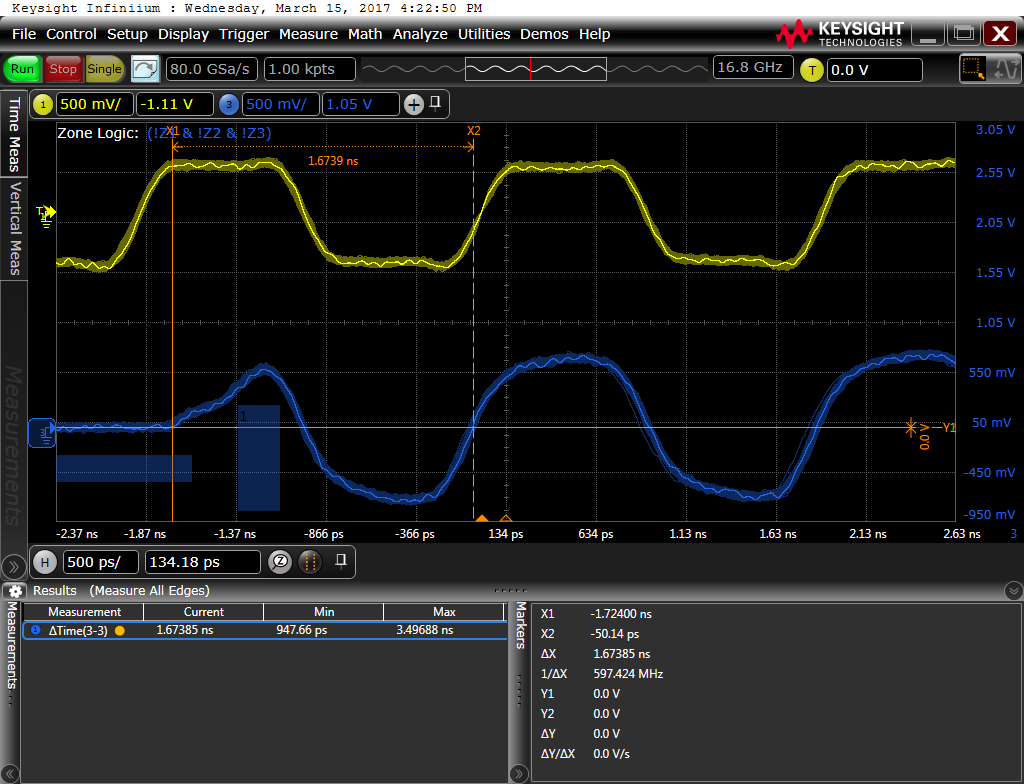

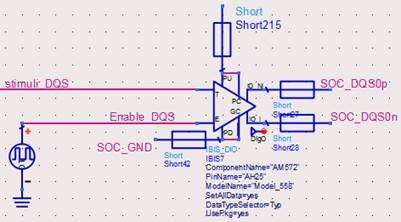

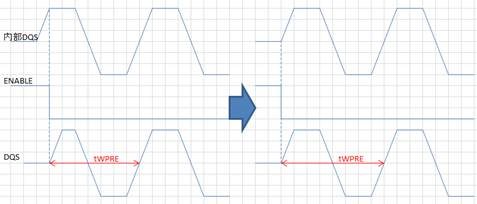

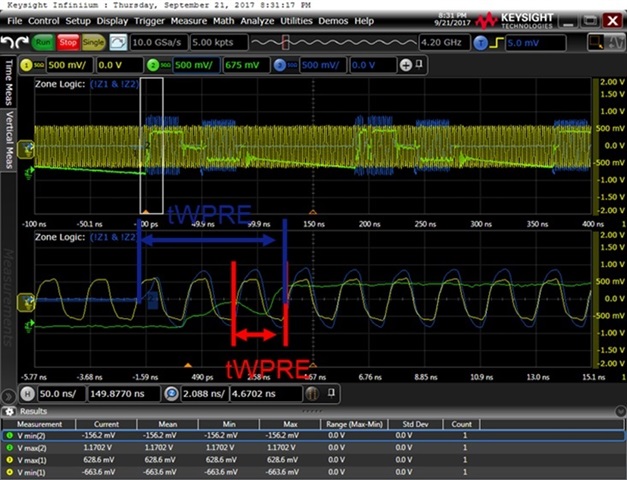

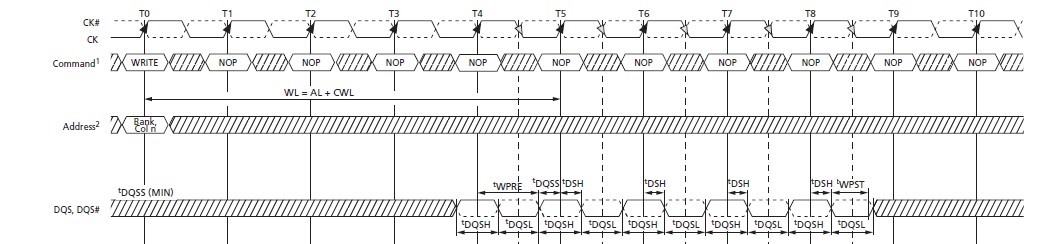

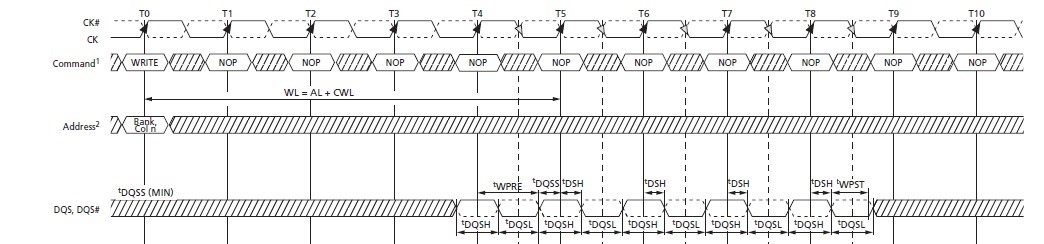

我们的客户在 AM572x DDR3合规性测试的 tWPRE 时间内失败。

tWPRE 部分的 DQS 的启动较晚,不符合 tWPRE (0.9*tck)的最小值。

请确认以下波形模式。

黄色:CK 信号

蓝色:DQS 信号

采取了以下对策、但在这两种情况下 tWPRE 的时间都不符合规范。

DDR_Term 位的变化

SDRAM_DRIVE 位的变化

PHY_INOP_CLKOUT 位和 PHY_REG_CTRL_SLAVE_RATIO0位的更改

CTRL_CORE_CONTRAL_DDRCACH2_0寄存器的 DDR3CH2_PART6_I[7:5]位的更改

CTRL_CORE_CONTRAL_DDRCH2_1寄存器的 DDRCH2_PART4B_I[7:5]位的更改

CTRL_CORE_CONTRAL_DDRCH2_1寄存器的 DDRCH2_PART4B_I[7:5]位的更改

7.I 将 Ω Ω 的端子电阻从39k Ω 更改为51k Ω。

有两个问题。

如何增加 DQS 的 tWPRE 部分或加快 tWPRE 的上升时间?

请告诉我如何操作。

tWPRE 时序不符合其他使用 AM572x 的用户的规格的问题是否未发生?

此致、

新义郎