您好!

我们使用 AM3352 GPMC 访问 FPGA (同步)、需要对进行一些澄清

GPMC 芯片选择 tw (csnV)时序。

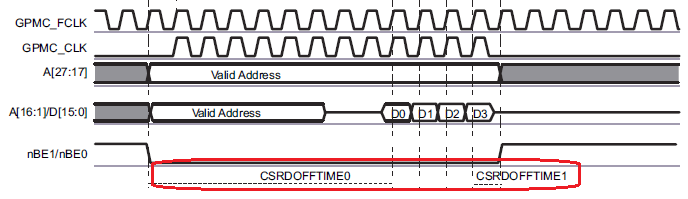

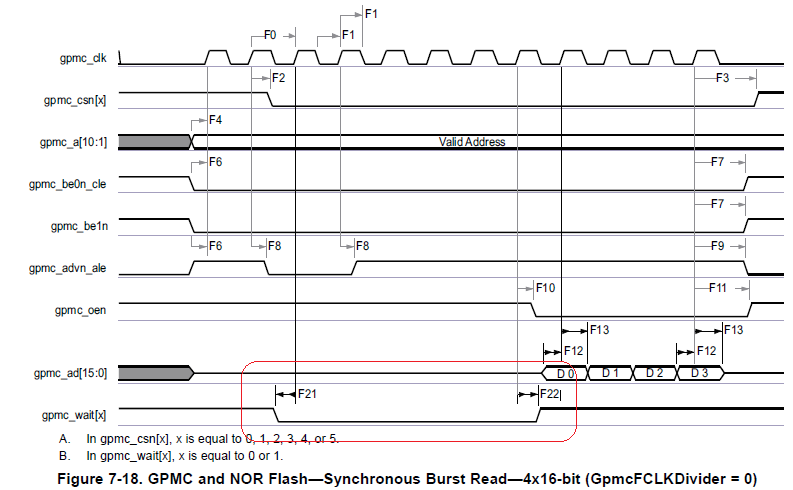

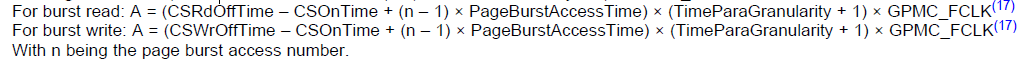

我们无法理解同步多(突发)读取(图7-20)的原因

CSRDOFFTIME 被分成两个部分(CSRDOFFTIME0和 CSRDOFFTIME1)

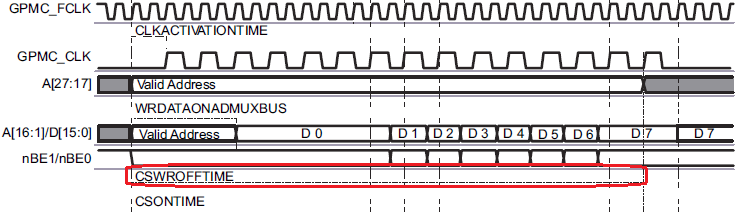

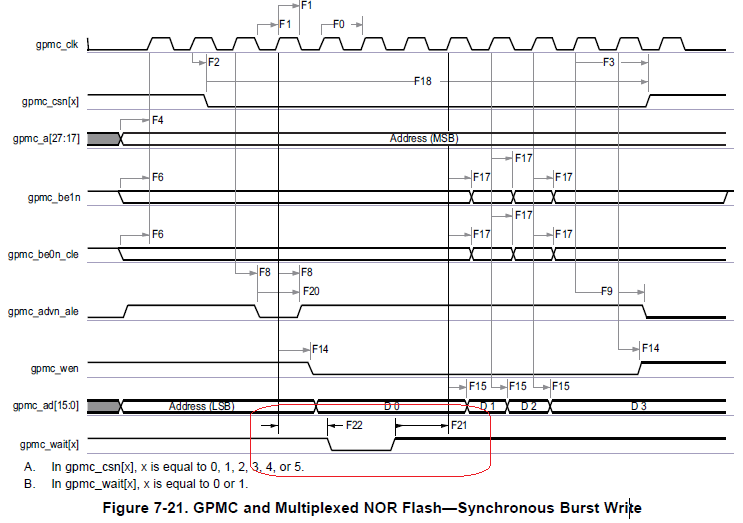

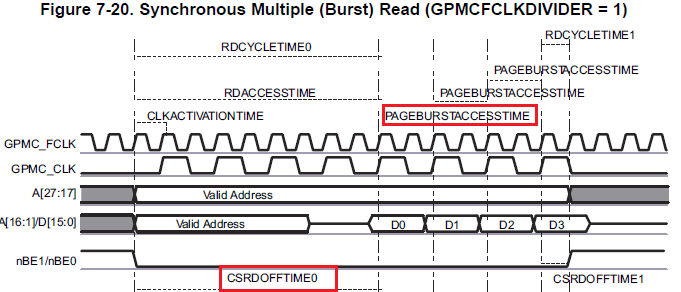

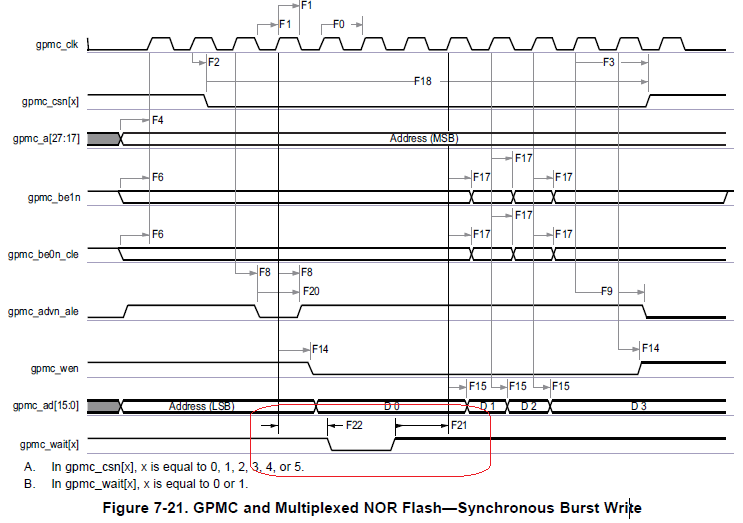

而同步多(突发)写入(图7-22)有一个 CSWROFFTIME?

同步多(突发)读取:

同步多(突发)写入:

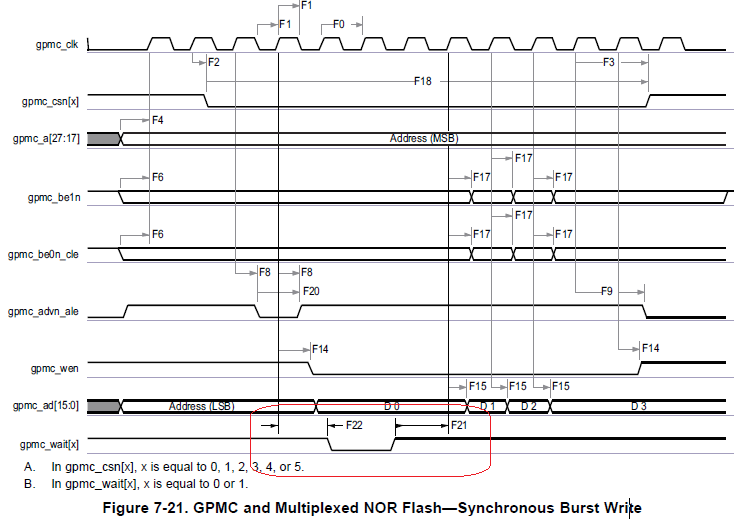

根据数据表"表7-22"、片选脉冲持续时间 tw (csnV)为

使用以下公式计算得出。

A =(CSRdOffTime–CSROnTime +(n–1)×PageBurstAccessTime)×(TimeParaGranularity + 1)×GPMC_FCLK

使用上面的等式、可以使用的差值来计算突发时间

CSOffTime 和 CSOnTime、我们相信这将是一个巨大的价值。

在实际设计中、我们需要遵循数据表计算和

TRM 手册(图7-20/图7-22)?

此致

库米