工具/软件:Linux

您好 Gurus、

我在基于 AM4377的定制板上工作。

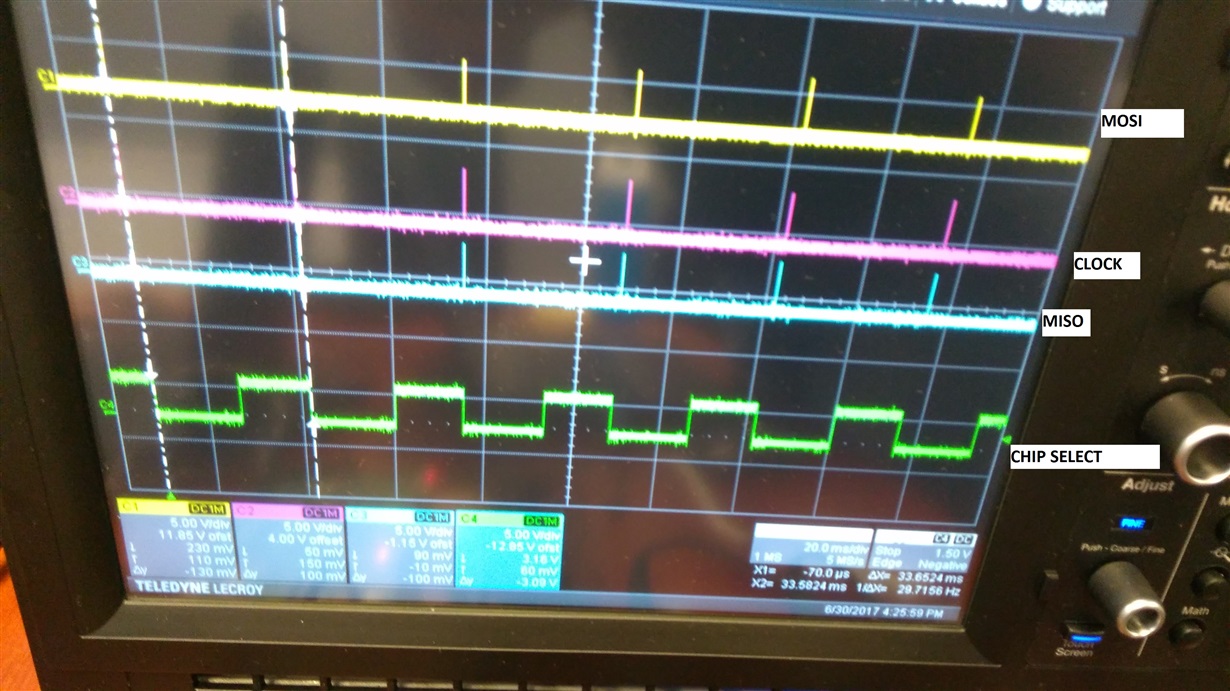

我面临与 SPI 芯片选择时序相关的问题、其中芯片选择在较长的时间内保持低电平和高电平。

我想让芯片选择在发送和接收到与 FPGA 从器件之间的32位数据(32个时钟周期)后变为高电平。(除了 t lead 和 t lag 延迟。)

SPI 使能(置位)是自动的。

我尝试了芯片选择切换(TCS0)的各种时间控制、但没有运气、并且持续时间保持不变。

芯片选择时间控制这

2位字段定义 CS 之间的接口时钟周期数

切换和 SPI 时钟的第一个或最后一个边沿。

0h (R/W)= 0.5时钟周期

1h (R/W)= 1.5个时钟周期

2h (R/W)= 2.5时钟周期

3h (R/W)= 3.5时钟周期

芯片选择持续时间在0.5、1.5、2.5和3.5个时钟周期内保持不变。

下图为您提供了有关时钟、MISO 和 MOSI 的芯片选择行为的更好概念。

那么、您能帮我更好地控制芯片选择的时序吗?

提前感谢。

此致

Rohit。