工具/软件:Code Composer Studio

你(们)好

我 要配置共享内存(MSMCRAM)。

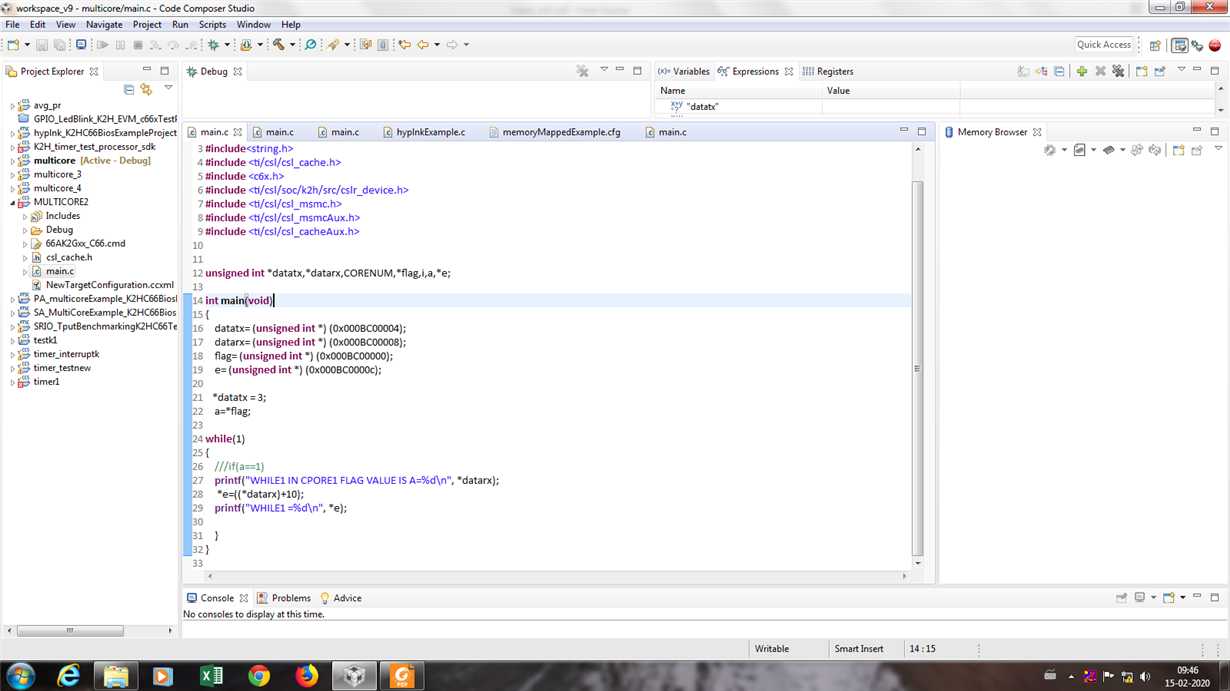

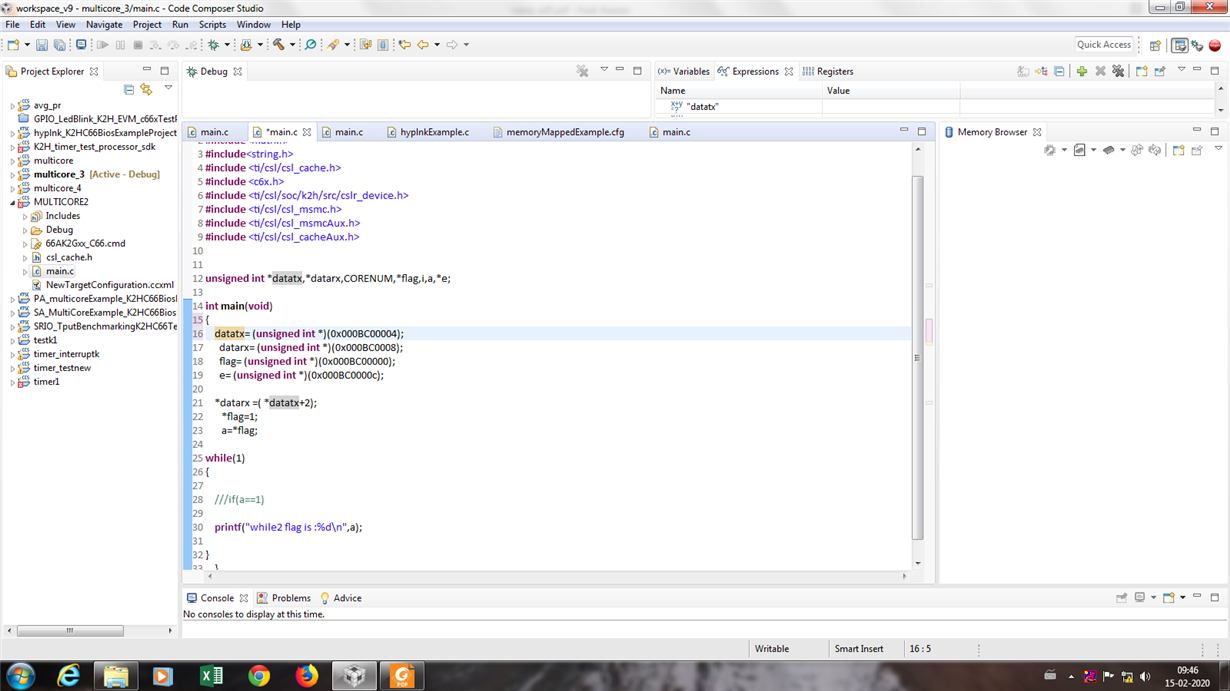

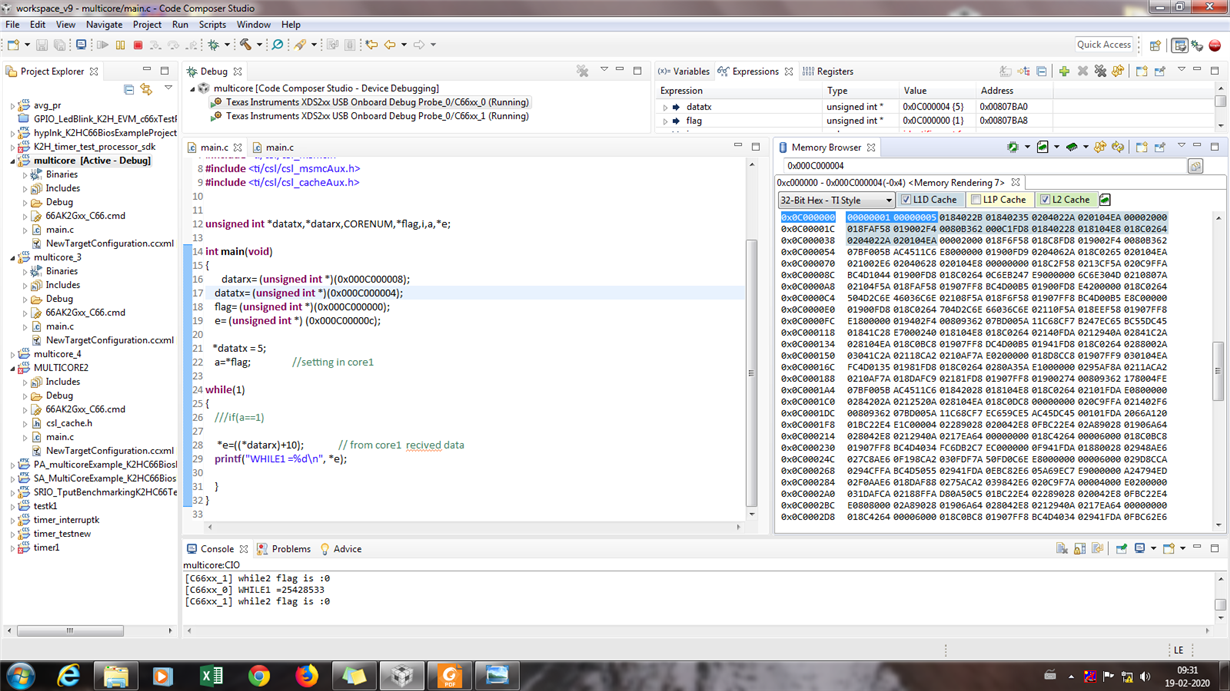

我正在使用多核处理器 i.e、我想使用两个内核 我有两个不同的项目、 一个在 core_0中、另一个在 core_1中、 在 CORE_0中、有一些 数据应该在 CORE_1中使用、同样、数据被 CORE_0使用 、因为我使用 MSM RAM 从两个处理器访问数据。

2.在数据表中为从 0XC000000到 C5FFFFF 的 MSMRAM 定义了地址是否可以 使用指针来使用该内存? 或者我应该 配置任何其他寄存器吗?

3.我 正在直接使用地址、但 两个内核中的该地址未提取数据、我是否应该在.cfg 文件中配置 MSM 的任何存储器? 和.c 自拍?

如果 您必须参考,是否有人可以建议我如何配置 MSMRAM 和共享任何示例项目?

谢谢、此致

KAVYA M U