数据表(SPRSP58A–2022年6月–2022年11月修订)和 TRM (SPRUIV7A–2022年5月–2022年11月修订)似乎不同意 OLDI/LVDS 信号的命名约定。 这是故意的吗? 能否提供一些有关这些信号相关性的说明?

谢谢、

Stuart

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

数据表(SPRSP58A–2022年6月–2022年11月修订)和 TRM (SPRUIV7A–2022年5月–2022年11月修订)似乎不同意 OLDI/LVDS 信号的命名约定。 这是故意的吗? 能否提供一些有关这些信号相关性的说明?

谢谢、

Stuart

我们无法从这份答复中了解很多内容。 您能否澄清他尝试提出的解决 方案。

我们想知道 、从 A0到 A7的 OLDI 对是否可以归类为以下类型

和映射信号,如下所述。

将 MPU_OLDI_A0_P 更改为 MPU_OLDI0_A0_P

将 MPU_OLDI_A0_N 更改为 MPU_OLDI0_A0_N

将 MPU_OLDI_A1_P 更改为 MPU_OLDI0_A1_P

将 MPU_OLDI_A1_N 更改为 MPU_OLDI0_A1_N

将 MPU_OLDI_A2_P 更改为 MPU_OLDI0_A2_P

将 MPU_OLDI_A2_N 更改为 MPU_OLDI0_A2_N

将 MPU_OLDI_A3_P 更改为 MPU_OLDI0_A3_P

将 MPU_OLDI_A3_N 更改为 MPU_OLDI0_A3_N

将 MPU_OLDI_CLK0_P 更改为 MPU_OLDI0_CLK_P

将 MPU_OLDI_CLK0_N 更改为 MPU_OLDI0_CLK_N

将 MPU_OLDI_A4_P 更改为 MPU_OLDI1_A0_P

将 MPU_OLDI_A4_N 更改为 MPU_OLDI1_A0_N

将 MPU_OLDI_A5_P 更改为 MPU_OLDI1_A1_P

将 MPU_OLDI_A5_N 更改为 MPU_OLDI1_A1_N

将 MPU_OLDI_A6_P 更改为 MPU_OLDI1_A2_P

将 MPU_OLDI_A6_N 更改为 MPU_OLDI1_A2_N

MPU_OLDI_A7_P 至 MPU_OLDI1_A3_P

将 MPU_OLDI_A7_N 更改为 MPU_OLDI1_A3_N

将 MPU_OLDI_CLK1_P 更改为 MPU_OLDI1_CLK_P

将 MPU_OLDI_CLK1_N 更改为 MPU_OLDI1_CLK_N

您好、Sreenivasa、

这是 Carrier 的 Srinivas Tummalapalli。

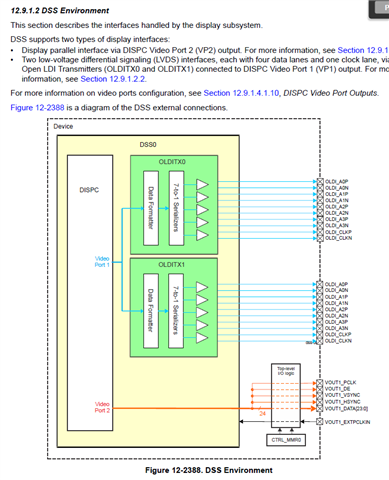

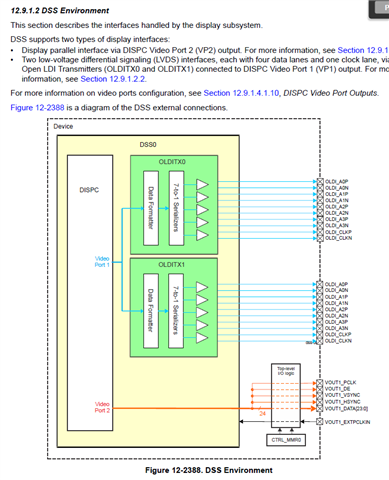

根据图12-2388 AM62x TRM、 AM62x Sitara MPU 具有两个与 LVDS 发送器并行的 Open LDI OLDITX0和 OLDITX1、每个都具有一个4通道接口和时钟。

根据我们的用例-对于更高分辨率的显示屏、这两个发送器可在双模模式下使用、以将时钟速率降低一半。 我们的显示屏需要单个4通道接口。

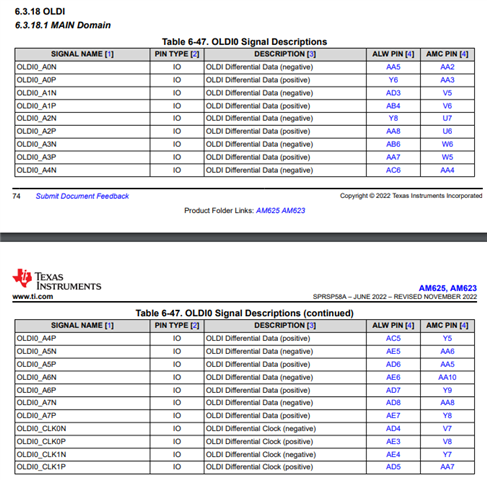

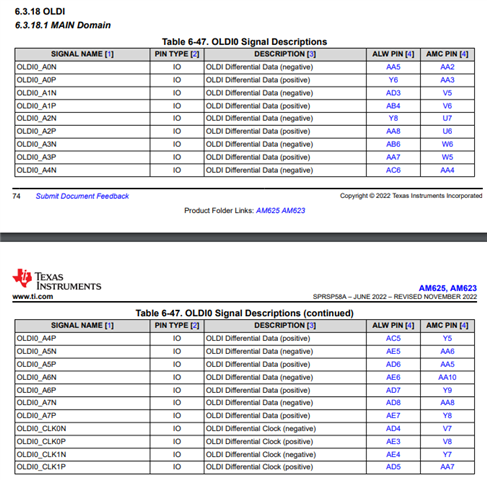

我们认为、当 TI 在 AM62x 数据表的表6-47中将这些信号命名为"错误/不匹配"时、可能会出现错误/不匹配-因为它仅指 OLDI0、从不指 OLDI1。

OLDI0是图12-2388的 OLDITX0部分:AM62x 数据表中也应有一个 OLDI1表、其中包含与 OLDTX1接口中的信号相对应的 OLDI1信号名称。

例如、我们如何确保 " MPU_OLDI_A4_P"对应于"MPU_OLDI1_A0_P"、因为 AM62x 数据表中没有提到它?

我们希望确保原理图在各自的 OLDIx 接口中更准确地反映出来、因此我们计划按如下方式更改符号、端口和信号名称:

我们对 OLDI0和 OLDI1`的以下假设是否正确? 如果是、您还能在 AM62x 数据表中反映吗?

将 MPU_OLDI_A0_P 更改为 MPU_OLDI0_A0_P

将 MPU_OLDI_A0_N 更改为 MPU_OLDI0_A0_N

将 MPU_OLDI_A1_P 更改为 MPU_OLDI0_A1_P

将 MPU_OLDI_A1_N 更改为 MPU_OLDI0_A1_N

将 MPU_OLDI_A2_P 更改为 MPU_OLDI0_A2_P

将 MPU_OLDI_A2_N 更改为 MPU_OLDI0_A2_N

将 MPU_OLDI_A3_P 更改为 MPU_OLDI0_A3_P

将 MPU_OLDI_A3_N 更改为 MPU_OLDI0_A3_N

将 MPU_OLDI_CLK0_P 更改为 MPU_OLDI0_CLK_P

将 MPU_OLDI_CLK0_N 更改为 MPU_OLDI0_CLK_N

将 MPU_OLDI_A4_P 更改为 MPU_OLDI1_A0_P

将 MPU_OLDI_A4_N 更改为 MPU_OLDI1_A0_N

将 MPU_OLDI_A5_P 更改为 MPU_OLDI1_A1_P

将 MPU_OLDI_A5_N 更改为 MPU_OLDI1_A1_N

将 MPU_OLDI_A6_P 更改为 MPU_OLDI1_A2_P

将 MPU_OLDI_A6_N 更改为 MPU_OLDI1_A2_N

MPU_OLDI_A7_P 至 MPU_OLDI1_A3_P

将 MPU_OLDI_A7_N 更改为 MPU_OLDI1_A3_N

将 MPU_OLDI_CLK1_P 更改为 MPU_OLDI1_CLK_P

将 MPU_OLDI_CLK1_N 更改为 MPU_OLDI1_CLK_N

您好 Srinivas Tummalapalli

晚上好。

感谢您对 OLDI 接口的看法。

据我了解 、我们有一个 OLDI 接口实例、如上图所示。

我可能需要与展示专家核实理由、以便分别展示两个单一链接。

以下是 OLDI 的2个用例

8通道用例-分为奇数和偶数个数

(36) AM625:将 LCD 连接到 AM625x -处理器论坛-处理器- TI E2E 支持论坛

4通道用例-显示镜

如果可能,请使用2个 LVDS 显示器,其中4个用于显示器1,另4个用于显示器2 ???

是的、可以连接两个显示屏并在单链路模式下使用 LVDS。 但是、由于硬件限制、两个显示屏都将被镜像。

如果我们同时使用两个显示器,我可以播放两个不同的视频,不是????

否、视频 将重复播放。

如前所述、命名约定取决于客户。 请确保您了解上述可能的用例、并确保进行正确的信号连接。

此致、

Sreenivasa

您好、Premalatha、

感谢您的输入和附加查询。

我相信 Andrei 之前已经确认了您对使用偶数和奇数像素的问题、我总结了上述内容、包括 Andrei 确认的线程链接。

以下配置 已经过测试、可以正常工作。 (TI 或3P)

我将总结您希望以的方式表示 OLDI 信号的功能。

在双模配置中、OLDI0分别发送奇数信号、OLDI1分别发送偶数信号

2.在镜像模式配置中,OLDI0和 OLDI1发送相同的信号。

请开始新的主题、询问 OLDI 驱动程序信息、以便我分配给可以提供支持的专家。

此致、

Sreenivasa

您好、Premalatha、

感谢您的参与

[引用 userid="526885" URL"~/support/processors-group/processors/f/processors-forum/1197483/am625-oldi-lvds-naming-mismatch-between-datasheet-and-trm/4525951 #4525951"]我们在 e2e 论坛中收到了响应、即"A0-A3对应奇数对和 A4-A7偶数对"。 请告知我们这是否正常。[/报价]请遵循 E2E 主题建议。

[引用 userid="526885" URL"~/support/processors-group/processors/f/processors-forum/1197483/am625-oldi-lvds-naming-mismatch-between-datasheet-and-trm/4525951 #4525951"]但 AM62xx 的哪些引脚对应于 OLDI 0、哪些引脚对应于 OLDI1? 是我们想要知道是否有相同的支持文档。[/quot]让我在内部与团队核实一下。

当我有一些答案时、我将更新该主题、但我建议您遵循 E2E 主题建议。

此致、

Sreenivasa