尊敬的团队:

在我们找到的引导流程之后、在 R5内核中设置了 CPSR 的 A 位、处理器 Linux SDK 版本为8.4。 这是正常的吗? 您是否发现此问题?

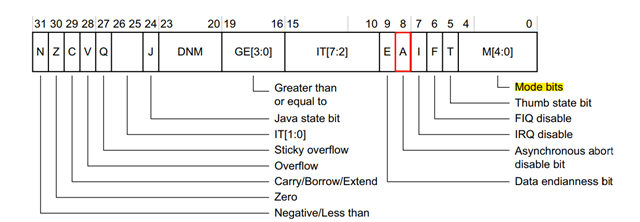

如图所示、该位 由某些异常自动置位、是特权软件写入的、因此发生了一些异常。

谢谢。

jimin.li

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的团队:

在我们找到的引导流程之后、在 R5内核中设置了 CPSR 的 A 位、处理器 Linux SDK 版本为8.4。 这是正常的吗? 您是否发现此问题?

如图所示、该位 由某些异常自动置位、是特权软件写入的、因此发生了一些异常。

谢谢。

jimin.li

尊敬的洪先生:

感谢您的回复!

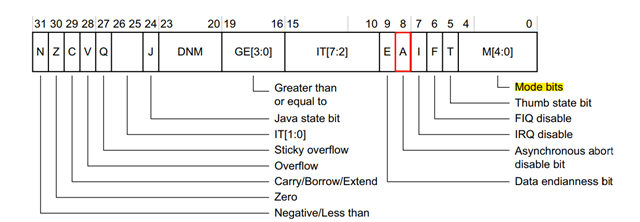

因此、 此位表示 屏蔽异步中止、而不会 发生某些异常。

无论在内核或引导中此位是否始终为1?不需要将此位设置为0?

当 a bit=CPSR[8]=1 =>异步中止被屏蔽时。

谢谢,

jimin.li