主题中讨论的其他器件:DRA829、 TDA4VL、 AM68、 TDA4VH、 AM69

要使其与 器件型号兼容、需要对 Jacinto SDK 进行哪些更改

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

摘要

Jacinto7 TDA4系列在其 SoC 中包含大量基于用例和应用的变体。

每个系列的 SDK 均提供对超集器件的支持–

SDK"开箱即用"支持 a)最快速度等级、以及 b) SoC 的全套功能。

对于给定的终端应用、用户负责修改 SDK、以符合终端应用要求并仅利用特定器件型号可用的功能/速度的方式对器件进行配置。

例如、

此常见问题解答 重点介绍了用户可能需要定制 SDK 的方面–以便为给定应用中不需要的功能(即使某个器件型号提供了该功能)节省功耗 如果 SoC 系列中的器件之间存在此类差异、则需要在 SDK 上进行更改、以使软件产品与这些子集器件兼容。

这将简化客户终端的 SDK 集成过程。

通过比较这两款器件、我们发现以下器件之间存在一些差异/修改。

注意:以下提到的更改直接适用于 RTOS 和 Linux SDK 8.6。 对于其他 SDK、请通过参考以下更改进行调整。

1.减少解除武装、复员和重返社会的情况

J721s2的某些子 集器件(例如 TDA4AL88、TDA4VL21等)与其超集器件(有2个)相比、仅有1个 DDR 实例。 因此、应进行以下修改、以使 SDK 与1个 DDR 实例兼容。

注意:有关 DDR 实例减小的更改仅发生在 u-boot 中。 只需对 VISION_APPS 进行细微修改

Boot tested on J721s2-EVM.

---

diff --git a/arch/arm/dts/k3-j721s2-ddr-evm-lp4-4266.dtsi b/arch/arm/dts/k3-j721s2-ddr-evm-lp4-4266.dtsi

index c91576bf09..8fbe202c75 100644

--- a/arch/arm/dts/k3-j721s2-ddr-evm-lp4-4266.dtsi

+++ b/arch/arm/dts/k3-j721s2-ddr-evm-lp4-4266.dtsi

@@ -14,7 +14,7 @@

#define MULTI_DDR_CFG_INTRLV_SIZE 11

#define MULTI_DDR_CFG_ECC_ENABLE 0

#define MULTI_DDR_CFG_HYBRID_SELECT 0

-#define MULTI_DDR_CFG_EMIFS_ACTIVE 3

+#define MULTI_DDR_CFG_EMIFS_ACTIVE 1

#define DDRSS0_CTL_00_DATA 0x00000B00

#define DDRSS0_CTL_01_DATA 0x00000000

diff --git a/arch/arm/dts/k3-j721s2-ddr.dtsi b/arch/arm/dts/k3-j721s2-ddr.dtsi

index 6a244fb7ac..7dabc2999b 100644

--- a/arch/arm/dts/k3-j721s2-ddr.dtsi

+++ b/arch/arm/dts/k3-j721s2-ddr.dtsi

@@ -2230,6 +2230,7 @@

};

memorycontroller1: memorycontroller@29b0000 {

+ status = "disabled";

compatible = "ti,j721s2-ddrss";

reg = <0x0 0x029b0000 0x0 0x4000>,

<0x0 0x0114000 0x0 0x100>;

diff --git a/arch/arm/dts/k3-j721s2-som-p0.dtsi b/arch/arm/dts/k3-j721s2-som-p0.dtsi

index f3080e948e..9e91110d90 100644

--- a/arch/arm/dts/k3-j721s2-som-p0.dtsi

+++ b/arch/arm/dts/k3-j721s2-som-p0.dtsi

@@ -13,9 +13,9 @@

/ {

memory@80000000 {

device_type = "memory";

- /* 16 GB RAM */

+ /* 8 GB RAM */

reg = <0x00 0x80000000 0x00 0x80000000>,

- <0x08 0x80000000 0x03 0x80000000>;

+ <0x08 0x80000000 0x01 0x80000000>;

};

/* Reserving memory regions still pending */

diff --git a/board/ti/j721s2/evm.c b/board/ti/j721s2/evm.c

index 90b7ca1150..51e50fa9c5 100644

--- a/board/ti/j721s2/evm.c

+++ b/board/ti/j721s2/evm.c

@@ -67,8 +67,8 @@ int dram_init_banksize(void)

#ifdef CONFIG_PHYS_64BIT

/* Bank 1 declares the memory available in the DDR high region */

gd->bd->bi_dram[1].start = CONFIG_SYS_SDRAM_BASE1;

- gd->bd->bi_dram[1].size = 0x37fffffff;

- gd->ram_size = 0x400000000;

+ gd->bd->bi_dram[1].size = 0x17fffffff;

+ gd->ram_size = 0x200000000;

#endif

return 0;

--

2.17.1

diff --git a/utils/perf_stats/src/app_perf_stats_freertos.c b/utils/perf_stats/src/app_perf_stats_freertos.c

index 2c63699..cd6805a 100644

--- a/utils/perf_stats/src/app_perf_stats_freertos.c

+++ b/utils/perf_stats/src/app_perf_stats_freertos.c

@@ -88,7 +88,7 @@

#if defined(SOC_J721E) || defined(SOC_AM62A)

#define APP_PERF_NUM_DDR_INSTANCES (1u)

#elif defined (SOC_J721S2)

-#define APP_PERF_NUM_DDR_INSTANCES (2u)

+#define APP_PERF_NUM_DDR_INSTANCES (1u)

#elif defined (SOC_J784S4)

#define APP_PERF_NUM_DDR_INSTANCES (4u)

#endif

@@ -631,7 +631,7 @@ void appPerfStatsDdrStatsReadCounters(uint32_t *val0, uint32_t *val1, uint32_t *

cnt3[0] = (volatile uint32_t *)0x02980110;

#endif

- #if defined(SOC_J721S2) || defined(SOC_J784S4)

+ #if defined(SOC_J784S4)

cnt_sel[1] = (volatile uint32_t *)0x029A0100;

cnt0[1] = (volatile uint32_t *)0x029A0104;

cnt1[1] = (volatile uint32_t *)0x029A0108;

验证:

检查 u-boot 日志、如下所示

U-Boot 2021.01-00002-g7f1139c55f

(4月26 2023 - 15:38:23 +0530)

SoC:J721S2 SR1.0 GP

型号:Texas Instruments J721S2 EVM

电路板:J721S2X-PM1-SOM 修订版 E1

DRAM:8 GiB

闪存:0字节

MMC:MMC@4f80000:0、MMC@4fb0000:1

输入:串行@2880000

2.根据速度等级或者功耗优化改变内核的时钟频率

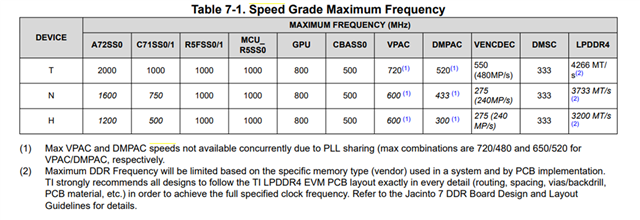

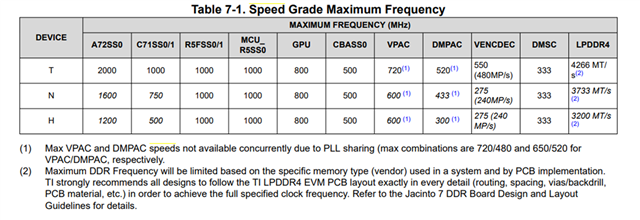

根据速度等级/功耗优化、内核运行时的时钟频率会发生变化。 下表显示了 J721s2的速度等级 T、N 和 H 的一个此类示例

要更改与某个内核关联的时钟频率、请按照以下步骤操作。

1.从超集器件的 TRM (时钟部分)中确定与该内核相关的时钟源/PLL 和分频器。

2.根据 PLL 修改分频器,使最终输出时钟符合速度等级。

下面是一个如何为 TDA4VL21更改 C7x 内核时钟的示例。 PLL 标识为 MAIN_PLL7 HSDIV0。

所做的更改如下所示。

diff --git a/packages/ti/drv/sciclient/src/rm_pm_hal/pm/soc/j721s2/clocks.c b/packages/ti/drv/sciclient/src/rm_pm_hal/pm/soc/j721s2/clocks.c

index 2122081..7438db5 100644

--- a/packages/ti/drv/sciclient/src/rm_pm_hal/pm/soc/j721s2/clocks.c

+++ b/packages/ti/drv/sciclient/src/rm_pm_hal/pm/soc/j721s2/clocks.c

@@ -5160,7 +5160,7 @@ static const struct clk_data_div_reg clk_data_hsdiv0_16fft_main_6_hsdiv0 = {

static const struct clk_data_div_reg clk_data_hsdiv0_16fft_main_7_hsdiv0 = {

.data_div = {

.n = 128,

- .default_div = 2,

+ .default_div = 4,

},

.reg = 0x00680000UL + (0x1000UL * 7UL) + 0x80UL + (0x4UL * 0UL),

.bit = 0,此处、C7x 内核的时钟从1GHz 降低到500MHz。

根据速度等级和功耗优化的组合、可以对其他内核/HWA 执行类似的操作。

验证 命令:

k3conf dump clock 8 k3conf dump clock 11

输出:

C7x 内核时钟值为500MHz。

|-----------------------------------------------------------------------------------------------------------------------| | Device ID | Clock ID | Clock Name | Status | Clock Frequency | |-----------------------------------------------------------------------------------------------------------------------| | 8 | 0 | DEV_COMPUTE_CLUSTER0_C71SS0_0_C7X_CLK | CLK_STATE_READY | 500000000 | | 8 | 1 | DEV_COMPUTE_CLUSTER0_C71SS0_0_PLL_CTRL_CLK | CLK_STATE_READY | 500000000 | | 8 | 3 | DEV_COMPUTE_CLUSTER0_C71SS0_0_C7X_DIVH_CLK4_OBSCLK_OUT_CLK | CLK_STATE_READY | 0 | |-----------------------------------------------------------------------------------------------------------------------| |-------------------------------------------------------------------------------------------------------| | Device ID | Clock ID | Clock Name | Status | Clock Frequency | |-------------------------------------------------------------------------------------------------------| | 11 | 0 | DEV_COMPUTE_CLUSTER0_C71SS1_0_C7X_CLK | CLK_STATE_READY | 500000000 | | 11 | 1 | DEV_COMPUTE_CLUSTER0_C71SS1_0_PLL_CTRL_CLK | CLK_STATE_READY | 500000000 | |-------------------------------------------------------------------------------------------------------|

3.禁用/移除其他内核

TDA4AL88和 TDA4VL21等子集是 四核 R5器件、而其超集则是六核器件。 还有其他只有1个 C7x 内核的子集。

在 u-boot、Linux 和 vision_apps 中需要对相同的内容进行更改。

例如、可以按如下所示删除 MCU3_0 (或) main_r5fs1

diff --git a/arch/arm/dts/k3-j721s2-common-proc-board.dts b/arch/arm/dts/k3-j721s2-common-proc-board.dts

index 5b7e33490f..ffd9c8568b 100644

--- a/arch/arm/dts/k3-j721s2-common-proc-board.dts

+++ b/arch/arm/dts/k3-j721s2-common-proc-board.dts

@@ -32,8 +32,6 @@

remoteproc1 = &mcu_r5fss0_core1;

remoteproc2 = &main_r5fss0_core0;

remoteproc3 = &main_r5fss0_core1;

- remoteproc4 = &main_r5fss1_core0;

- remoteproc5 = &main_r5fss1_core1;

remoteproc6 = &c71_0;

remoteproc7 = &c71_1;

};

diff --git a/arch/arm/dts/k3-j721s2-main.dtsi b/arch/arm/dts/k3-j721s2-main.dtsi

index 18e5113336..d9bf23b1e9 100644

--- a/arch/arm/dts/k3-j721s2-main.dtsi

+++ b/arch/arm/dts/k3-j721s2-main.dtsi

@@ -1152,46 +1152,6 @@

};

};

- main_r5fss1: r5fss@5e00000 {

- compatible = "ti,j721s2-r5fss";

- ti,cluster-mode = <0>;

- #address-cells = <1>;

- #size-cells = <1>;

- ranges = <0x5e00000 0x00 0x5e00000 0x20000>,

- <0x5f00000 0x00 0x5f00000 0x20000>;

- power-domains = <&k3_pds 278 TI_SCI_PD_EXCLUSIVE>;

-

- main_r5fss1_core0: r5f@5e00000 {

- compatible = "ti,j721s2-r5f";

- reg = <0x5e00000 0x00010000>,

- <0x5e10000 0x00010000>;

- reg-names = "atcm", "btcm";

- ti,sci = <&sms>;

- ti,sci-dev-id = <281>;

- ti,sci-proc-ids = <0x08 0xff>;

- resets = <&k3_reset 281 1>;

- firmware-name = "j721s2-main-r5f1_0-fw";

- ti,atcm-enable = <1>;

- ti,btcm-enable = <1>;

- ti,loczrama = <1>;

- };

-

- main_r5fss1_core1: r5f@5f00000 {

- compatible = "ti,j721s2-r5f";

- reg = <0x5f00000 0x00010000>,

- <0x5f10000 0x00010000>;

- reg-names = "atcm", "btcm";

- ti,sci = <&sms>;

- ti,sci-dev-id = <282>;

- ti,sci-proc-ids = <0x09 0xff>;

- resets = <&k3_reset 282 1>;

- firmware-name = "j721s2-main-r5f1_1-fw";

- ti,atcm-enable = <1>;

- ti,btcm-enable = <1>;

- ti,loczrama = <1>;

- };

- };

-

c71_0: dsp@64800000 {

compatible = "ti,j721s2-c71-dsp";

reg = <0x00 0x64800000 0x00 0x00080000>,

diff --git a/arch/arm/dts/k3-j721s2-som-p0.dtsi b/arch/arm/dts/k3-j721s2-som-p0.dtsi

index f3080e948e..c4df1d51bd 100644

--- a/arch/arm/dts/k3-j721s2-som-p0.dtsi

+++ b/arch/arm/dts/k3-j721s2-som-p0.dtsi

@@ -78,30 +78,6 @@

no-map;

};

- main_r5fss1_core0_dma_memory_region: r5f-dma-memory@a4000000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa4000000 0x00 0x100000>;

- no-map;

- };

-

- main_r5fss1_core0_memory_region: r5f-memory@a4100000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa4100000 0x00 0xf00000>;

- no-map;

- };

-

- main_r5fss1_core1_dma_memory_region: r5f-dma-memory@a5000000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa5000000 0x00 0x100000>;

- no-map;

- };

-

- main_r5fss1_core1_memory_region: r5f-memory@a5100000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa5100000 0x00 0xf00000>;

- no-map;

- };

-

c71_0_dma_memory_region: c71-dma-memory@a6000000 {

compatible = "shared-dma-pool";

reg = <0x00 0xa6000000 0x00 0x100000>;

@@ -251,17 +227,7 @@

};

&mailbox0_cluster2 {

- interrupts = <428>;

-

- mbox_main_r5fss1_core0: mbox-main-r5fss1-core0 {

- ti,mbox-rx = <0 0 0>;

- ti,mbox-tx = <1 0 0>;

- };

-

- mbox_main_r5fss1_core1: mbox-main-r5fss1-core1 {

- ti,mbox-rx = <2 0 0>;

- ti,mbox-tx = <3 0 0>;

- };

+ status = "disabled";

};

&mailbox0_cluster3 {

@@ -382,18 +348,6 @@

<&main_r5fss0_core1_memory_region>;

};

-&main_r5fss1_core0 {

- mboxes = <&mailbox0_cluster2 &mbox_main_r5fss1_core0>;

- memory-region = <&main_r5fss1_core0_dma_memory_region>,

- <&main_r5fss1_core0_memory_region>;

-};

-

-&main_r5fss1_core1 {

- mboxes = <&mailbox0_cluster2 &mbox_main_r5fss1_core1>;

- memory-region = <&main_r5fss1_core1_dma_memory_region>,

- <&main_r5fss1_core1_memory_region>;

-};

-

&c71_0 {

mboxes = <&mailbox0_cluster4 &mbox_c71_0>;

memory-region = <&c71_0_dma_memory_region>,

diff --git a/arch/arm/dts/k3-j721s2-common-proc-board.dts b/arch/arm/dts/k3-j721s2-common-proc-board.dts

index 5b7e33490f..ffd9c8568b 100644

--- a/arch/arm/dts/k3-j721s2-common-proc-board.dts

+++ b/arch/arm/dts/k3-j721s2-common-proc-board.dts

@@ -32,8 +32,6 @@

remoteproc1 = &mcu_r5fss0_core1;

remoteproc2 = &main_r5fss0_core0;

remoteproc3 = &main_r5fss0_core1;

- remoteproc4 = &main_r5fss1_core0;

- remoteproc5 = &main_r5fss1_core1;

remoteproc6 = &c71_0;

remoteproc7 = &c71_1;

};

diff --git a/arch/arm/dts/k3-j721s2-main.dtsi b/arch/arm/dts/k3-j721s2-main.dtsi

index 18e5113336..d9bf23b1e9 100644

--- a/arch/arm/dts/k3-j721s2-main.dtsi

+++ b/arch/arm/dts/k3-j721s2-main.dtsi

@@ -1152,46 +1152,6 @@

};

};

- main_r5fss1: r5fss@5e00000 {

- compatible = "ti,j721s2-r5fss";

- ti,cluster-mode = <0>;

- #address-cells = <1>;

- #size-cells = <1>;

- ranges = <0x5e00000 0x00 0x5e00000 0x20000>,

- <0x5f00000 0x00 0x5f00000 0x20000>;

- power-domains = <&k3_pds 278 TI_SCI_PD_EXCLUSIVE>;

-

- main_r5fss1_core0: r5f@5e00000 {

- compatible = "ti,j721s2-r5f";

- reg = <0x5e00000 0x00010000>,

- <0x5e10000 0x00010000>;

- reg-names = "atcm", "btcm";

- ti,sci = <&sms>;

- ti,sci-dev-id = <281>;

- ti,sci-proc-ids = <0x08 0xff>;

- resets = <&k3_reset 281 1>;

- firmware-name = "j721s2-main-r5f1_0-fw";

- ti,atcm-enable = <1>;

- ti,btcm-enable = <1>;

- ti,loczrama = <1>;

- };

-

- main_r5fss1_core1: r5f@5f00000 {

- compatible = "ti,j721s2-r5f";

- reg = <0x5f00000 0x00010000>,

- <0x5f10000 0x00010000>;

- reg-names = "atcm", "btcm";

- ti,sci = <&sms>;

- ti,sci-dev-id = <282>;

- ti,sci-proc-ids = <0x09 0xff>;

- resets = <&k3_reset 282 1>;

- firmware-name = "j721s2-main-r5f1_1-fw";

- ti,atcm-enable = <1>;

- ti,btcm-enable = <1>;

- ti,loczrama = <1>;

- };

- };

-

c71_0: dsp@64800000 {

compatible = "ti,j721s2-c71-dsp";

reg = <0x00 0x64800000 0x00 0x00080000>,

diff --git a/arch/arm/dts/k3-j721s2-som-p0.dtsi b/arch/arm/dts/k3-j721s2-som-p0.dtsi

index f3080e948e..c4df1d51bd 100644

--- a/arch/arm/dts/k3-j721s2-som-p0.dtsi

+++ b/arch/arm/dts/k3-j721s2-som-p0.dtsi

@@ -78,30 +78,6 @@

no-map;

};

- main_r5fss1_core0_dma_memory_region: r5f-dma-memory@a4000000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa4000000 0x00 0x100000>;

- no-map;

- };

-

- main_r5fss1_core0_memory_region: r5f-memory@a4100000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa4100000 0x00 0xf00000>;

- no-map;

- };

-

- main_r5fss1_core1_dma_memory_region: r5f-dma-memory@a5000000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa5000000 0x00 0x100000>;

- no-map;

- };

-

- main_r5fss1_core1_memory_region: r5f-memory@a5100000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa5100000 0x00 0xf00000>;

- no-map;

- };

-

c71_0_dma_memory_region: c71-dma-memory@a6000000 {

compatible = "shared-dma-pool";

reg = <0x00 0xa6000000 0x00 0x100000>;

@@ -251,17 +227,7 @@

};

&mailbox0_cluster2 {

- interrupts = <428>;

-

- mbox_main_r5fss1_core0: mbox-main-r5fss1-core0 {

- ti,mbox-rx = <0 0 0>;

- ti,mbox-tx = <1 0 0>;

- };

-

- mbox_main_r5fss1_core1: mbox-main-r5fss1-core1 {

- ti,mbox-rx = <2 0 0>;

- ti,mbox-tx = <3 0 0>;

- };

+ status = "disabled";

};

&mailbox0_cluster3 {

@@ -382,18 +348,6 @@

<&main_r5fss0_core1_memory_region>;

};

-&main_r5fss1_core0 {

- mboxes = <&mailbox0_cluster2 &mbox_main_r5fss1_core0>;

- memory-region = <&main_r5fss1_core0_dma_memory_region>,

- <&main_r5fss1_core0_memory_region>;

-};

-

-&main_r5fss1_core1 {

- mboxes = <&mailbox0_cluster2 &mbox_main_r5fss1_core1>;

- memory-region = <&main_r5fss1_core1_dma_memory_region>,

- <&main_r5fss1_core1_memory_region>;

-};

-

&c71_0 {

mboxes = <&mailbox0_cluster4 &mbox_c71_0>;

memory-region = <&c71_0_dma_memory_region>,

diff --git a/platform/j721s2/rtos/app_mem_map.h b/platform/j721s2/rtos/app_mem_map.h

index 4f1c7f6..e562580 100755

--- a/platform/j721s2/rtos/app_mem_map.h

+++ b/platform/j721s2/rtos/app_mem_map.h

@@ -127,22 +127,6 @@

#define DDR_MCU2_1_DTS_ADDR (0xA4100000u)

#define DDR_MCU2_1_DTS_SIZE (0x01F00000u)

-/* DDR for MCU3_0 for Linux IPC [ size 1024.00 KB ] */

-#define DDR_MCU3_0_IPC_ADDR (0xA6000000u)

-#define DDR_MCU3_0_IPC_SIZE (0x00100000u)

-

-/* DDR for MCU3_0 for all sections, used for reserving memory in DTS file [ size 15.00 MB ] */

-#define DDR_MCU3_0_DTS_ADDR (0xA6100000u)

-#define DDR_MCU3_0_DTS_SIZE (0x00F00000u)

-

-/* DDR for MCU3_1 for Linux IPC [ size 1024.00 KB ] */

-#define DDR_MCU3_1_IPC_ADDR (0xA7000000u)

-#define DDR_MCU3_1_IPC_SIZE (0x00100000u)

-

-/* DDR for MCU3_1 for all sections, used for reserving memory in DTS file [ size 15.00 MB ] */

-#define DDR_MCU3_1_DTS_ADDR (0xA7100000u)

-#define DDR_MCU3_1_DTS_SIZE (0x00F00000u)

-

/* Memory for IPC Vring's. MUST be non-cached or cache-coherent [ size 32.00 MB ] */

#define IPC_VRING_MEM_ADDR (0xA8000000u)

#define IPC_VRING_MEM_SIZE (0x02000000u)

@@ -195,14 +179,6 @@

#define DDR_MCU2_1_LOCAL_HEAP_ADDR (0xDA000000u)

#define DDR_MCU2_1_LOCAL_HEAP_SIZE (0x01000000u)

-/* DDR for MCU3_0 for local heap [ size 8.00 MB ] */

-#define DDR_MCU3_0_LOCAL_HEAP_ADDR (0xDB000000u)

-#define DDR_MCU3_0_LOCAL_HEAP_SIZE (0x00800000u)

-

-/* DDR for MCU3_1 for local heap [ size 8.00 MB ] */

-#define DDR_MCU3_1_LOCAL_HEAP_ADDR (0xDB800000u)

-#define DDR_MCU3_1_LOCAL_HEAP_SIZE (0x00800000u)

-

/* DDR for c7x_1 for Scratch Memory [ size 368.00 MB ] */

#define DDR_C7X_1_SCRATCH_ADDR (0x100000000u)

#define DDR_C7X_1_SCRATCH_SIZE (0x17000000u)

diff --git a/platform/j721s2/rtos/gen_linker_mem_map.py b/platform/j721s2/rtos/gen_linker_mem_map.py

index 56725bc..c19fd69 100755

--- a/platform/j721s2/rtos/gen_linker_mem_map.py

+++ b/platform/j721s2/rtos/gen_linker_mem_map.py

@@ -79,7 +79,7 @@

# This will generate linker command file at below folders

# ./<cpu name>/linker_mem_map.cmd

#

-# Here CPU name is mpu1, c7x_1, c7x_2, mcu1_0, mcu2_0, mcu3_0

+# Here CPU name is mpu1, c7x_1, c7x_2, mcu1_0, mcu2_0

#

#

from ti_psdk_rtos_tools import *

@@ -193,16 +193,6 @@ mcu2_1_ddr_resource_table_addr = mcu2_1_ddr_ipc_addr + linux_ddr_ipc_size;

mcu2_1_ddr_addr = mcu2_1_ddr_resource_table_addr + linux_ddr_resource_table_size;

mcu2_1_ddr_size = 32*MB - (mcu2_1_ddr_addr-mcu2_1_ddr_ipc_addr);

-mcu3_0_ddr_ipc_addr = mcu2_1_ddr_addr + mcu2_1_ddr_size;

-mcu3_0_ddr_resource_table_addr = mcu3_0_ddr_ipc_addr + linux_ddr_ipc_size;

-mcu3_0_ddr_addr = mcu3_0_ddr_resource_table_addr + linux_ddr_resource_table_size;

-mcu3_0_ddr_size = 16*MB - (mcu3_0_ddr_addr-mcu3_0_ddr_ipc_addr);

-

-mcu3_1_ddr_ipc_addr = mcu3_0_ddr_addr + mcu3_0_ddr_size;

-mcu3_1_ddr_resource_table_addr = mcu3_1_ddr_ipc_addr + linux_ddr_ipc_size;

-mcu3_1_ddr_addr = mcu3_1_ddr_resource_table_addr + linux_ddr_resource_table_size;

-mcu3_1_ddr_size = 16*MB - (mcu3_1_ddr_addr-mcu3_1_ddr_ipc_addr);

-

#

# DDR memory allocation for various shared memories

#

@@ -253,10 +243,6 @@ mcu2_0_ddr_local_heap_addr = mcu1_1_ddr_local_heap_addr + mcu1_1_ddr_local_heap

mcu2_0_ddr_local_heap_size = 16*MB;

mcu2_1_ddr_local_heap_addr = mcu2_0_ddr_local_heap_addr + mcu2_0_ddr_local_heap_size;

mcu2_1_ddr_local_heap_size = 16*MB;

-mcu3_0_ddr_local_heap_addr = mcu2_1_ddr_local_heap_addr + mcu2_1_ddr_local_heap_size;

-mcu3_0_ddr_local_heap_size = 8*MB;

-mcu3_1_ddr_local_heap_addr = mcu3_0_ddr_local_heap_addr + mcu3_0_ddr_local_heap_size;

-mcu3_1_ddr_local_heap_size = 8*MB;

c7x_1_ddr_scratch_addr = ddr_mem_addr_hi;

c7x_1_ddr_scratch_size = 368*MB;

@@ -343,26 +329,6 @@ mcu2_1_ddr_total.concat(mcu2_1_ddr_resource_table);

mcu2_1_ddr_total.concat(mcu2_1_ddr);

mcu2_1_ddr_total.setDtsName("vision_apps_main_r5fss0_core1_memory_region", "vision-apps-r5f-memory");

-mcu3_0_ddr_ipc = MemSection("DDR_MCU3_0_IPC", "RWIX", mcu3_0_ddr_ipc_addr, linux_ddr_ipc_size, "DDR for MCU3_0 for Linux IPC");

-mcu3_0_ddr_ipc.setDtsName("vision_apps_main_r5fss1_core0_dma_memory_region", "vision-apps-r5f-dma-memory");

-mcu3_0_ddr_resource_table = MemSection("DDR_MCU3_0_RESOURCE_TABLE", "RWIX", mcu3_0_ddr_resource_table_addr, linux_ddr_resource_table_size, "DDR for MCU3_0 for Linux resource table");

-mcu3_0_ddr = MemSection("DDR_MCU3_0", "RWIX", mcu3_0_ddr_addr, mcu3_0_ddr_size, "DDR for MCU3_0 for code/data");

-mcu3_0_ddr_local_heap = MemSection("DDR_MCU3_0_LOCAL_HEAP", "RWIX", mcu3_0_ddr_local_heap_addr, mcu3_0_ddr_local_heap_size, "DDR for MCU3_0 for local heap");

-mcu3_0_ddr_total = MemSection("DDR_MCU3_0_DTS", "", 0, 0, "DDR for MCU3_0 for all sections, used for reserving memory in DTS file");

-mcu3_0_ddr_total.concat(mcu3_0_ddr_resource_table);

-mcu3_0_ddr_total.concat(mcu3_0_ddr);

-mcu3_0_ddr_total.setDtsName("vision_apps_main_r5fss1_core0_memory_region", "vision-apps-r5f-memory");

-

-mcu3_1_ddr_ipc = MemSection("DDR_MCU3_1_IPC", "RWIX", mcu3_1_ddr_ipc_addr, linux_ddr_ipc_size, "DDR for MCU3_1 for Linux IPC");

-mcu3_1_ddr_ipc.setDtsName("vision_apps_main_r5fss1_core1_dma_memory_region", "vision-apps-r5f-dma-memory");

-mcu3_1_ddr_resource_table = MemSection("DDR_MCU3_1_RESOURCE_TABLE", "RWIX", mcu3_1_ddr_resource_table_addr, linux_ddr_resource_table_size, "DDR for MCU3_1 for Linux resource table");

-mcu3_1_ddr = MemSection("DDR_MCU3_1", "RWIX", mcu3_1_ddr_addr, mcu3_1_ddr_size, "DDR for MCU3_1 for code/data");

-mcu3_1_ddr_local_heap = MemSection("DDR_MCU3_1_LOCAL_HEAP", "RWIX", mcu3_1_ddr_local_heap_addr, mcu3_1_ddr_local_heap_size, "DDR for MCU3_1 for local heap");

-mcu3_1_ddr_total = MemSection("DDR_MCU3_1_DTS", "", 0, 0, "DDR for MCU3_1 for all sections, used for reserving memory in DTS file");

-mcu3_1_ddr_total.concat(mcu3_1_ddr_resource_table);

-mcu3_1_ddr_total.concat(mcu3_1_ddr);

-mcu3_1_ddr_total.setDtsName("vision_apps_main_r5fss1_core1_memory_region", "vision-apps-r5f-memory");

-

c7x_2_ddr_ipc = MemSection("DDR_C7x_2_IPC", "RWIX", c7x_2_ddr_ipc_addr, linux_ddr_ipc_size, "DDR for C7x_2 for Linux IPC");

c7x_2_ddr_ipc.setDtsName("vision_apps_c71_1_dma_memory_region", "vision-apps-c71_1-dma-memory");

c7x_2_ddr_resource_table = MemSection("DDR_C7x_2_RESOURCE_TABLE", "RWIX", c7x_2_ddr_resource_table_addr, linux_ddr_resource_table_size, "DDR for C7x_2 for Linux resource table");

@@ -422,8 +388,6 @@ vision_apps_core_heaps_lo = MemSection("DDR_VISION_APPS_CORE_HEAPS_LO_DTS", "",

vision_apps_core_heaps_lo.concat(mcu1_0_ddr_local_heap);

vision_apps_core_heaps_lo.concat(mcu2_0_ddr_local_heap);

vision_apps_core_heaps_lo.concat(mcu2_1_ddr_local_heap);

-vision_apps_core_heaps_lo.concat(mcu3_0_ddr_local_heap);

-vision_apps_core_heaps_lo.concat(mcu3_1_ddr_local_heap);

vision_apps_core_heaps_lo.setDtsName("vision_apps_core_heaps_lo", "vision-apps-core-heap-memory-lo");

c7x_1_ddr_local_heap_phy = MemSection("DDR_C7X_1_LOCAL_HEAP", "RWIX", ddr_mem_addr_hi_phy, (c7x_1_ddr_scratch_size + c7x_1_ddr_local_heap_size + c7x_2_ddr_scratch_size + c7x_2_ddr_local_heap_size), "DDR for c7x_1, c7x_2 for scratch memory and local heap");

@@ -498,34 +462,6 @@ mcu2_1_mmap.addMemSection( ddr_shared_mem );

mcu2_1_mmap.addMemSection( mcu2_1_main_ocram );

mcu2_1_mmap.checkOverlap();

-mcu3_0_mmap = MemoryMap("mcu3_0");

-mcu3_0_mmap.addMemSection( mcu_r5f_tcma_vecs );

-mcu3_0_mmap.addMemSection( mcu_r5f_tcma );

-mcu3_0_mmap.addMemSection( r5f_tcmb0 );

-mcu3_0_mmap.addMemSection( mcu3_0_ddr_ipc );

-mcu3_0_mmap.addMemSection( mcu3_0_ddr_resource_table );

-mcu3_0_mmap.addMemSection( mcu3_0_ddr );

-mcu3_0_mmap.addMemSection( app_log_mem );

-mcu3_0_mmap.addMemSection( tiovx_obj_desc_mem );

-mcu3_0_mmap.addMemSection( ipc_vring_mem );

-mcu3_0_mmap.addMemSection( mcu3_0_ddr_local_heap );

-mcu3_0_mmap.addMemSection( ddr_shared_mem );

-mcu3_0_mmap.checkOverlap();

-

-mcu3_1_mmap = MemoryMap("mcu3_1");

-mcu3_1_mmap.addMemSection( mcu_r5f_tcma_vecs );

-mcu3_1_mmap.addMemSection( mcu_r5f_tcma );

-mcu3_1_mmap.addMemSection( r5f_tcmb0 );

-mcu3_1_mmap.addMemSection( mcu3_1_ddr_ipc );

-mcu3_1_mmap.addMemSection( mcu3_1_ddr_resource_table );

-mcu3_1_mmap.addMemSection( mcu3_1_ddr );

-mcu3_1_mmap.addMemSection( app_log_mem );

-mcu3_1_mmap.addMemSection( tiovx_obj_desc_mem );

-mcu3_1_mmap.addMemSection( ipc_vring_mem );

-mcu3_1_mmap.addMemSection( mcu3_1_ddr_local_heap );

-mcu3_1_mmap.addMemSection( ddr_shared_mem );

-mcu3_1_mmap.checkOverlap();

-

c7x_1_mmap = MemoryMap("c7x_1");

c7x_1_mmap.addMemSection( c7x_1_l2 );

c7x_1_mmap.addMemSection( c7x_1_l1 );

@@ -585,14 +521,6 @@ html_mmap.addMemSection( mcu2_1_ddr_ipc );

html_mmap.addMemSection( mcu2_1_ddr_resource_table );

html_mmap.addMemSection( mcu2_1_ddr );

html_mmap.addMemSection( mcu2_1_ddr_local_heap );

-html_mmap.addMemSection( mcu3_0_ddr_ipc );

-html_mmap.addMemSection( mcu3_0_ddr_resource_table );

-html_mmap.addMemSection( mcu3_0_ddr );

-html_mmap.addMemSection( mcu3_0_ddr_local_heap );

-html_mmap.addMemSection( mcu3_1_ddr_ipc );

-html_mmap.addMemSection( mcu3_1_ddr_resource_table );

-html_mmap.addMemSection( mcu3_1_ddr );

-html_mmap.addMemSection( mcu3_1_ddr_local_heap );

html_mmap.addMemSection( c7x_1_ddr_ipc );

html_mmap.addMemSection( c7x_1_ddr_resource_table );

html_mmap.addMemSection( c7x_1_ddr_boot );

@@ -628,16 +556,12 @@ c_header_mmap.addMemSection( mcu1_0_ddr_ipc );

c_header_mmap.addMemSection( mcu1_1_ddr_ipc );

c_header_mmap.addMemSection( mcu2_0_ddr_ipc );

c_header_mmap.addMemSection( mcu2_1_ddr_ipc );

-c_header_mmap.addMemSection( mcu3_0_ddr_ipc );

-c_header_mmap.addMemSection( mcu3_1_ddr_ipc );

c_header_mmap.addMemSection( c7x_1_ddr_ipc );

c_header_mmap.addMemSection( c7x_2_ddr_ipc );

c_header_mmap.addMemSection( mcu1_0_ddr_total );

c_header_mmap.addMemSection( mcu1_1_ddr_total );

c_header_mmap.addMemSection( mcu2_0_ddr_total );

c_header_mmap.addMemSection( mcu2_1_ddr_total );

-c_header_mmap.addMemSection( mcu3_0_ddr_total );

-c_header_mmap.addMemSection( mcu3_1_ddr_total );

c_header_mmap.addMemSection( c7x_1_ddr_total );

c_header_mmap.addMemSection( c7x_2_ddr_total );

@@ -645,8 +569,6 @@ c_header_mmap.addMemSection( mcu1_0_ddr_local_heap);

c_header_mmap.addMemSection( mcu1_1_ddr_local_heap);

c_header_mmap.addMemSection( mcu2_0_ddr_local_heap);

c_header_mmap.addMemSection( mcu2_1_ddr_local_heap);

-c_header_mmap.addMemSection( mcu3_0_ddr_local_heap);

-c_header_mmap.addMemSection( mcu3_1_ddr_local_heap);

c_header_mmap.addMemSection( c7x_1_ddr_local_heap);

c_header_mmap.addMemSection( c7x_1_ddr_scratch);

c_header_mmap.addMemSection( c7x_2_ddr_local_heap);

@@ -672,10 +594,6 @@ dts_mmap.addMemSection( mcu2_0_ddr_ipc );

dts_mmap.addMemSection( mcu2_0_ddr_total );

dts_mmap.addMemSection( mcu2_1_ddr_ipc );

dts_mmap.addMemSection( mcu2_1_ddr_total );

-dts_mmap.addMemSection( mcu3_0_ddr_ipc );

-dts_mmap.addMemSection( mcu3_0_ddr_total );

-dts_mmap.addMemSection( mcu3_1_ddr_ipc );

-dts_mmap.addMemSection( mcu3_1_ddr_total );

dts_mmap.addMemSection( c7x_1_ddr_ipc );

dts_mmap.addMemSection( c7x_1_ddr_total );

dts_mmap.addMemSection( c7x_2_ddr_ipc );

@@ -696,8 +614,6 @@ LinkerCmdFile(mcu1_0_mmap, "./mcu1_0/linker_mem_map.cmd").export();

LinkerCmdFile(mcu1_1_mmap, "./mcu1_1/linker_mem_map.cmd").export();

LinkerCmdFile(mcu2_0_mmap, "./mcu2_0/linker_mem_map.cmd").export();

LinkerCmdFile(mcu2_1_mmap, "./mcu2_1/linker_mem_map.cmd").export();

-LinkerCmdFile(mcu3_0_mmap, "./mcu3_0/linker_mem_map.cmd").export();

-LinkerCmdFile(mcu3_1_mmap, "./mcu3_1/linker_mem_map.cmd").export();

HtmlMmapTable(html_mmap, "./system_memory_map.html").export();

diff --git a/platform/j721s2/rtos/k3-j721s2-rtos-memory-map.dtsi b/platform/j721s2/rtos/k3-j721s2-rtos-memory-map.dtsi

index 86855a6..214590f 100644

--- a/platform/j721s2/rtos/k3-j721s2-rtos-memory-map.dtsi

+++ b/platform/j721s2/rtos/k3-j721s2-rtos-memory-map.dtsi

@@ -4,7 +4,7 @@

* IMPORTANT NOTE: Follow below instructions to apply the updated memory map to linux dtsi file,

*

* 1. Copy the memory sections, from the generated dts file, to the file shown below under reserved_memory: reserved-memory { ... }

- * ${LINUX_KERNEL_PATH}/arch/arm64/boot/dts/ti/k3-j721s2-rtos-memory-map.dtsi

+ * ${LINUX_KERNEL_PATH}/arch/arm64/boot/dts/ti/k3-j721e-rtos-memory-map.dtsi

*

* 2. Rebuild the dtb, dtbo from PSDK Linux install directory

* make linux-dtbs

@@ -55,26 +55,6 @@

reg = <0x00 0xa4100000 0x00 0x01f00000>;

no-map;

};

- vision_apps_main_r5fss1_core0_dma_memory_region: vision-apps-r5f-dma-memory@a6000000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa6000000 0x00 0x00100000>;

- no-map;

- };

- vision_apps_main_r5fss1_core0_memory_region: vision-apps-r5f-memory@a6100000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa6100000 0x00 0x00f00000>;

- no-map;

- };

- vision_apps_main_r5fss1_core1_dma_memory_region: vision-apps-r5f-dma-memory@a7000000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa7000000 0x00 0x00100000>;

- no-map;

- };

- vision_apps_main_r5fss1_core1_memory_region: vision-apps-r5f-memory@a7100000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa7100000 0x00 0x00f00000>;

- no-map;

- };

vision_apps_rtos_ipc_memory_region: vision-apps-rtos-ipc-memory-region@a8000000 {

compatible = "shared-dma-pool";

reg = <0x00 0xa8000000 0x00 0x02000000>;

@@ -111,7 +91,7 @@

};

vision_apps_core_heaps_lo: vision-apps-core-heap-memory-lo@d8000000 {

compatible = "shared-dma-pool";

- reg = <0x00 0xd8000000 0x00 0x04000000>;

+ reg = <0x00 0xd8000000 0x00 0x03000000>;

no-map;

};

vision_apps_core_heaps_hi: vision-apps-core-heap-memory-hi@880000000 {

diff --git a/platform/j721s2/rtos/system_memory_map.html b/platform/j721s2/rtos/system_memory_map.html

index 1859f9b..57d49f5 100644

--- a/platform/j721s2/rtos/system_memory_map.html

+++ b/platform/j721s2/rtos/system_memory_map.html

@@ -192,54 +192,6 @@

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU2_1 for code/data</td>

</tr>

- <tr>

- <td class="tg-6sgx">DDR_MCU3_0_IPC</td>

- <td class="tg-6sgx">0xA6000000</td>

- <td class="tg-6sgx">0xA60FFFFF</td>

- <td class="tg-6sgx">1024.00 KB</td>

- <td class="tg-6sgx">RWIX</td>

- <td class="tg-6sgx">DDR for MCU3_0 for Linux IPC</td>

- </tr>

- <tr>

- <td class="tg-kftd">DDR_MCU3_0_RESOURCE_TABLE</td>

- <td class="tg-kftd">0xA6100000</td>

- <td class="tg-kftd">0xA61003FF</td>

- <td class="tg-kftd">1024 B</td>

- <td class="tg-kftd">RWIX</td>

- <td class="tg-kftd">DDR for MCU3_0 for Linux resource table</td>

- </tr>

- <tr>

- <td class="tg-6sgx">DDR_MCU3_0</td>

- <td class="tg-6sgx">0xA6100400</td>

- <td class="tg-6sgx">0xA6FFFFFF</td>

- <td class="tg-6sgx">15.00 MB</td>

- <td class="tg-6sgx">RWIX</td>

- <td class="tg-6sgx">DDR for MCU3_0 for code/data</td>

- </tr>

- <tr>

- <td class="tg-kftd">DDR_MCU3_1_IPC</td>

- <td class="tg-kftd">0xA7000000</td>

- <td class="tg-kftd">0xA70FFFFF</td>

- <td class="tg-kftd">1024.00 KB</td>

- <td class="tg-kftd">RWIX</td>

- <td class="tg-kftd">DDR for MCU3_1 for Linux IPC</td>

- </tr>

- <tr>

- <td class="tg-6sgx">DDR_MCU3_1_RESOURCE_TABLE</td>

- <td class="tg-6sgx">0xA7100000</td>

- <td class="tg-6sgx">0xA71003FF</td>

- <td class="tg-6sgx">1024 B</td>

- <td class="tg-6sgx">RWIX</td>

- <td class="tg-6sgx">DDR for MCU3_1 for Linux resource table</td>

- </tr>

- <tr>

- <td class="tg-kftd">DDR_MCU3_1</td>

- <td class="tg-kftd">0xA7100400</td>

- <td class="tg-kftd">0xA7FFFFFF</td>

- <td class="tg-kftd">15.00 MB</td>

- <td class="tg-kftd">RWIX</td>

- <td class="tg-kftd">DDR for MCU3_1 for code/data</td>

- </tr>

<tr>

<td class="tg-6sgx">IPC_VRING_MEM</td>

<td class="tg-6sgx">0xA8000000</td>

@@ -408,22 +360,6 @@

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU2_1 for local heap</td>

</tr>

- <tr>

- <td class="tg-kftd">DDR_MCU3_0_LOCAL_HEAP</td>

- <td class="tg-kftd">0xDB000000</td>

- <td class="tg-kftd">0xDB7FFFFF</td>

- <td class="tg-kftd"> 8.00 MB</td>

- <td class="tg-kftd">RWIX</td>

- <td class="tg-kftd">DDR for MCU3_0 for local heap</td>

- </tr>

- <tr>

- <td class="tg-6sgx">DDR_MCU3_1_LOCAL_HEAP</td>

- <td class="tg-6sgx">0xDB800000</td>

- <td class="tg-6sgx">0xDBFFFFFF</td>

- <td class="tg-6sgx"> 8.00 MB</td>

- <td class="tg-6sgx">RWIX</td>

- <td class="tg-6sgx">DDR for MCU3_1 for local heap</td>

- </tr>

<tr>

<td class="tg-kftd">DDR_C7X_1_SCRATCH</td>

<td class="tg-kftd">0x100000000</td>

验证 命令:

cat /proc/interrupts

输出:

在命令输入端看不到 main-r5fs1-core0中断

4.删除 驱动程序为禁用的 IP (GPU,EDP,CSITX 等)

子集器件需要删除一些硬件 IP。

例如:

a) 子集分析设备如 TDA4AL、GPU 不可用。 因此、为了从 SDK 中删除 GPU 支持、需要在 u-boot 和 Linux 内核上进行更改、如下所示。

diff --git a/arch/arm/dts/k3-j721s2.dtsi b/arch/arm/dts/k3-j721s2.dtsi index c25d0c2aff..d7c4f95f21 100644 --- a/arch/arm/dts/k3-j721s2.dtsi +++ b/arch/arm/dts/k3-j721s2.dtsi @@ -122,7 +122,6 @@ <0x00 0x70000000 0x00 0x70000000 0x00 0x00400000>, /* MSMC RAM */ <0x00 0x30000000 0x00 0x30000000 0x00 0x0c400000>, /* MAIN NAVSS */ <0x41 0x00000000 0x41 0x00000000 0x01 0x00000000>, /* PCIe1 DAT1 */ - <0x4e 0x20000000 0x4e 0x20000000 0x00 0x00080000>, /* GPU */ /* MCUSS_WKUP Range */ <0x00 0x28380000 0x00 0x28380000 0x00 0x03880000>,

diff --git a/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi b/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

index 69216fe05..8ee1a470e 100644

--- a/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

@@ -288,16 +288,6 @@

power-domains = <&k3_pds 358 TI_SCI_PD_EXCLUSIVE>;

};

- gpu: gpu@4e20000000 {

- compatible = "ti,j721s2-pvr", "img,pvr-bxs64";

- reg = <0x4e 0x20000000 0x00 0x80000>;

- interrupts = <GIC_SPI 24 IRQ_TYPE_LEVEL_HIGH>;

- power-domains = <&k3_pds 130 TI_SCI_PD_EXCLUSIVE>,

- <&k3_pds 373 TI_SCI_PD_EXCLUSIVE>;

- power-domain-names = "gpu_0", "gpucore_0";

- clocks = <&k3_clks 130 1>;

- };

-

main_gpio0: gpio@600000 {

compatible = "ti,j721e-gpio", "ti,keystone-gpio";

reg = <0x00 0x00600000 0x00 0x100>;

diff --git a/arch/arm64/boot/dts/ti/k3-j721s2.dtsi b/arch/arm64/boot/dts/ti/k3-j721s2.dtsi

index 75bc8dfac..dd2f0ebc8 100644

--- a/arch/arm64/boot/dts/ti/k3-j721s2.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-j721s2.dtsi

@@ -122,7 +122,6 @@

<0x00 0x70000000 0x00 0x70000000 0x00 0x00400000>, /* MSMC RAM */

<0x00 0x30000000 0x00 0x30000000 0x00 0x0c400000>, /* MAIN NAVSS */

<0x41 0x00000000 0x41 0x00000000 0x01 0x00000000>, /* PCIe1 DAT1 */

- <0x4e 0x20000000 0x4e 0x20000000 0x00 0x00080000>, /* GPU */

/* MCUSS_WKUP Range */

<0x00 0x28380000 0x00 0x28380000 0x00 0x03880000>,

验证 命令:

devmem2 0x4E20000018

输出:

内核崩溃

b) 对于 TDA4AL88等一些子集分析器件、EDP 不支持。 因此、为了 从 SDK 中删除 EDP 支持、需要在 Linux 内核上进行更改、如下所示。

diff --git a/arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dts b/arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dts

index b6158a27f..a8ad37a9a 100644

--- a/arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dts

+++ b/arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dts

@@ -148,19 +148,6 @@

regulator-always-on;

};

- dp0: dp0-connector {

- compatible = "dp-connector";

- label = "DP0";

- type = "full-size";

- dp-pwr-supply = <&dp0_pwr_3v3>;

-

- port {

- dp0_connector_in: endpoint {

- remote-endpoint = <&dp0_out>;

- };

- };

- };

-

panel {

compatible = "ti,panel-edp";

power-supply = <&dp1_pwr_3v3>;

@@ -626,13 +613,6 @@

#address-cells = <1>;

#size-cells = <0>;

- port@0 {

- reg = <0>;

- dpi0_out: endpoint {

- remote-endpoint = <&dp0_in>;

- };

- };

-

port@2 {

reg = <2>;

dpi2_out: endpoint {

@@ -673,31 +653,6 @@

};

};

-&mhdp {

- pinctrl-names = "default";

- pinctrl-0 = <&dp0_pins_default>;

- cdns,no-hpd;

-};

-

-&dp0_ports {

- #address-cells = <1>;

- #size-cells = <0>;

-

- port@0 {

- reg = <0>;

- dp0_in: endpoint {

- remote-endpoint = <&dpi0_out>;

- };

- };

-

- port@4 {

- reg = <4>;

- dp0_out: endpoint {

- remote-endpoint = <&dp0_connector_in>;

- };

- };

-};

-

&main_mcan0 {

status = "disabled";

};

diff --git a/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi b/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

index 69216fe05..8ee1a470e 100644

--- a/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

@@ -1493,32 +1443,6 @@

power-domains = <&k3_pds 346 TI_SCI_PD_EXCLUSIVE>;

};

- mhdp: dp-bridge@a000000 {

- compatible = "ti,j721e-mhdp8546";

- /*

- * Note: we do not map DPTX PHY area, as that is handled by

- * the PHY driver.

- */

- reg = <0x0 0xa000000 0x0 0x30a00>, /* DSS_EDP0_V2A_CORE_VP_REGS_APB */

- <0x0 0x4f40000 0x0 0x20>; /* DSS_EDP0_INTG_CFG_VP */

- reg-names = "mhdptx", "j721e-intg";

-

- clocks = <&k3_clks 156 19>;

-

- phys = <&torrent_phy_dp>;

- phy-names = "dpphy";

-

- interrupt-parent = <&gic500>;

- interrupts = <GIC_SPI 614 IRQ_TYPE_LEVEL_HIGH>;

-

- power-domains = <&k3_pds 156 TI_SCI_PD_EXCLUSIVE>;

-

- dp0_ports: ports {

- #address-cells = <1>;

- #size-cells = <0>;

- };

- };

-

dphy0: phy@4480000 {

compatible = "ti,j721e-dphy";

reg = <0x0 0x04480000 0x0 0x1000>;

验证 命令:

devmem2 0x04F4001C

输出:

内核崩溃

SBL 引导流程

对于 SBL 引导流程、用户需要参考以下针对 SDK 8.6的修改

1. 减少解除武装、复员和重返社会的情况

J721s2的某些子 集器件(例如 TDA4AL88、TDA4VL21等)与其超集器件(有2个)相比、仅有1个 DDR 实例。 因此、应进行以下修改、以使 SDK 与1个 DDR 实例兼容。

请注意: 与 DDR 寄存器相关的更改在 SBL 中完成、而 DDR 大小的配置应在 Linux 上完成。 只需对 VISION_APPS 进行细微修改

diff --git a/packages/ti/board/src/j721s2_evm/board_clock.c b/packages/ti/board/src/j721s2_evm/board_clock.c

index b7e6faf..1d5524b 100644

--- a/packages/ti/board/src/j721s2_evm/board_clock.c

+++ b/packages/ti/board/src/j721s2_evm/board_clock.c

@@ -98,9 +98,7 @@ uint32_t gBoardClkModuleMcuIDDeinitGroupl[] = {

uint32_t gBoardClkModuleMainIDInitGroup1[] = {

TISCI_DEV_DDR0,

- TISCI_DEV_DDR1,

TISCI_DEV_EMIF_DATA_0_VD,

- TISCI_DEV_EMIF_DATA_1_VD,

TISCI_DEV_MMCSD0,

TISCI_DEV_MMCSD1,

TISCI_DEV_GPIO4,

diff --git a/packages/ti/board/src/j721s2_evm/include/board_ddr.h b/packages/ti/board/src/j721s2_evm/include/board_ddr.h

index 60213e0..b75c22e 100644

--- a/packages/ti/board/src/j721s2_evm/include/board_ddr.h

+++ b/packages/ti/board/src/j721s2_evm/include/board_ddr.h

@@ -86,7 +86,7 @@ extern "C" {

#define BOARD_DDR_INSTANCE_0 (0U)

#define BOARD_DDR_INSTANCE_1 (1U)

-#define BOARD_DDR_INSTANCE_MAX (2U)

+#define BOARD_DDR_INSTANCE_MAX (1U)

#define BOARD_DDR_LOCK0 (0x115008U)

#define BOARD_DDR_LOCK1 (0x11500CU)

diff --git a/packages/ti/board/src/j721s2_evm/include/board_ddrRegInit.h b/packages/ti/board/src/j721s2_evm/include/board_ddrRegInit.h

index feec6d6..ddd2b4f 100644

--- a/packages/ti/board/src/j721s2_evm/include/board_ddrRegInit.h

+++ b/packages/ti/board/src/j721s2_evm/include/board_ddrRegInit.h

@@ -45,7 +45,7 @@

#define MULTI_DDR_CFG_INTRLV_SIZE 11

#define MULTI_DDR_CFG_ECC_ENABLE 0

#define MULTI_DDR_CFG_HYBRID_SELECT 0

-#define MULTI_DDR_CFG_EMIFS_ACTIVE 3

+#define MULTI_DDR_CFG_EMIFS_ACTIVE 1

uint32_t DDRSS0_ctlReg[] = {

0x00000B00U,

diff --git a/arch/arm64/boot/dts/ti/k3-j721s2-som-p0.dtsi b/arch/arm64/boot/dts/ti/k3-j721s2-som-p0.dtsi

index db1219b2b..725bc4481 100644

--- a/arch/arm64/boot/dts/ti/k3-j721s2-som-p0.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-j721s2-som-p0.dtsi

@@ -13,9 +13,9 @@

/ {

memory@80000000 {

device_type = "memory";

- /* 16 GB RAM */

+ /* 8 GB RAM */

reg = <0x00 0x80000000 0x00 0x80000000>,

- <0x08 0x80000000 0x03 0x80000000>;

+ <0x08 0x80000000 0x01 0x80000000>;

};

/* Reserving memory regions still pending */

@@ -469,3 +469,228 @@

};

};

};

diff --git a/utils/perf_stats/src/app_perf_stats_freertos.c b/utils/perf_stats/src/app_perf_stats_freertos.c

index 2c63699..cd6805a 100644

--- a/utils/perf_stats/src/app_perf_stats_freertos.c

+++ b/utils/perf_stats/src/app_perf_stats_freertos.c

@@ -88,7 +88,7 @@

#if defined(SOC_J721E) || defined(SOC_AM62A)

#define APP_PERF_NUM_DDR_INSTANCES (1u)

#elif defined (SOC_J721S2)

-#define APP_PERF_NUM_DDR_INSTANCES (2u)

+#define APP_PERF_NUM_DDR_INSTANCES (1u)

#elif defined (SOC_J784S4)

#define APP_PERF_NUM_DDR_INSTANCES (4u)

#endif

@@ -631,7 +631,7 @@ void appPerfStatsDdrStatsReadCounters(uint32_t *val0, uint32_t *val1, uint32_t *

cnt3[0] = (volatile uint32_t *)0x02980110;

#endif

- #if defined(SOC_J721S2) || defined(SOC_J784S4)

+ #if defined(SOC_J784S4)

cnt_sel[1] = (volatile uint32_t *)0x029A0100;

cnt0[1] = (volatile uint32_t *)0x029A0104;

cnt1[1] = (volatile uint32_t *)0x029A0108;

所需构建

cd ${PSDKLA}/

make linux-dtbs

Assuming the SOC is J721s2 (SDK 8.6)

cd ${PSDKRA}/pdk_j721s2_08_06_00_31/packages/ti/build/

make pdk_libs_clean BOARD=j721s2_evm

make pdk_libs BOARD=j721s2_evm

Assuming the SOC is J721s2 (SDK 8.6), Default SBL with MMCSD boot media

For custom SBL and different boot media, please adapt the build commands accordingly

cd ${PSDKRA}/pdk_j721s2_08_06_00_31/packages/ti/build/

make sbl_lib_mmcsd_hlos_clean BOARD=j721s2_evm

make sbl_mmcsd_img_hlos_clean BOARD=j721s2_evm

make sbl_lib_mmcsd_hlos BOARD=j721s2_evm

make sbl_mmcsd_img_hlos BOARD=j721s2_evm

Assuming SOC as J721s2 (SDK 8.6)

To Build vision_apps

=====================

cd ${PSDKRA}/vision_apps

make vision_apps_scrub

make vision_apps

To Build combined_app image

============================

cd ${PSDKRA}/pdk_j721s2_08_06_00_31/packages/ti/boot/sbl/tools/combined_appimage/

make clean BOARD=j721s2_evm

make BOARD=j721s2_evm HLOS_BOOT=optimized

验证 命令

root@j721s2-evm:~# grep MemTotal /proc/meminfo

MemTotal: 6418836 kB

root@j721s2-evm:~# free

total used free shared buff/cache available

Mem: 6418836 79556 6145748 9276 193532 6175444

Swap: 0 0 0

root@j721s2-evm:~#

2. 根据速度等级或者功耗优化改变内核的时钟频率

根据速度等级/功耗优化、内核运行时的时钟频率会发生变化。 下表显示了 J721s2的速度等级 T、N 和 H 的一个此类示例

要更改与某个内核关联的时钟频率、请按照以下步骤操作。

1.从超集器件的 TRM (时钟部分)中确定与该内核相关的时钟源/PLL 和分频器。

2.根据 PLL 修改分频器,使最终输出时钟符合速度等级。

以下是 如何更改 TDA4VL21的 C7x 内核的时钟 。 PLL 标识为 MAIN_PLL7 HSDIV0。

所做的更改如下所示。

diff --git a/packages/ti/drv/sciclient/src/rm_pm_hal/pm/soc/j721s2/clocks.c b/packages/ti/drv/sciclient/src/rm_pm_hal/pm/soc/j721s2/clocks.c

index 2122081..7438db5 100644

--- a/packages/ti/drv/sciclient/src/rm_pm_hal/pm/soc/j721s2/clocks.c

+++ b/packages/ti/drv/sciclient/src/rm_pm_hal/pm/soc/j721s2/clocks.c

@@ -5160,7 +5160,7 @@ static const struct clk_data_div_reg clk_data_hsdiv0_16fft_main_6_hsdiv0 = {

static const struct clk_data_div_reg clk_data_hsdiv0_16fft_main_7_hsdiv0 = {

.data_div = {

.n = 128,

- .default_div = 2,

+ .default_div = 4,

},

.reg = 0x00680000UL + (0x1000UL * 7UL) + 0x80UL + (0x4UL * 0UL),

.bit = 0,

此处、C7x 内核的时钟从1GHz 降低到500MHz。

所需构建

Assuming the SOC is J721s2 (SDK 8.6)

cd ${PSDKRA}/pdk_j721s2_08_06_00_31/packages/ti/build/

make pdk_libs_clean BOARD=j721s2_evm

make pdk_libs BOARD=j721s2_evm

Assuming SOC as J721s2 (SDK 8.6). DM is assumed to be ipc_echo_testb_freertos.

If a different DM is used, please use the command to rebuild that DM.

To Build DM

============

cd ${PSDKRA}/pdk_j721s2_08_06_00_31/packages/ti/build

make ipc_echo_testb_freertos_clean BOARD=j721s2_evm CORE=mcu1_0

make ipc_echo_testb_freertos BOARD=j721s2_evm CORE=mcu1_0

To Build combined_app image

============================

cd ${PSDKRA}/pdk_j721s2_08_06_00_31/packages/ti/boot/sbl/tools/combined_appimage/

make clean BOARD=j721s2_evm

make BOARD=j721s2_evm HLOS_BOOT=optimized

验证 命令:

k3conf dump clock 8 k3conf dump clock 11

输出:

C7x 内核时钟值为500MHz。

|-----------------------------------------------------------------------------------------------------------------------| | Device ID | Clock ID | Clock Name | Status | Clock Frequency | |-----------------------------------------------------------------------------------------------------------------------| | 8 | 0 | DEV_COMPUTE_CLUSTER0_C71SS0_0_C7X_CLK | CLK_STATE_READY | 500000000 | | 8 | 1 | DEV_COMPUTE_CLUSTER0_C71SS0_0_PLL_CTRL_CLK | CLK_STATE_READY | 500000000 | | 8 | 3 | DEV_COMPUTE_CLUSTER0_C71SS0_0_C7X_DIVH_CLK4_OBSCLK_OUT_CLK | CLK_STATE_READY | 0 | |-----------------------------------------------------------------------------------------------------------------------| |-------------------------------------------------------------------------------------------------------| | Device ID | Clock ID | Clock Name | Status | Clock Frequency | |-------------------------------------------------------------------------------------------------------| | 11 | 0 | DEV_COMPUTE_CLUSTER0_C71SS1_0_C7X_CLK | CLK_STATE_READY | 500000000 | | 11 | 1 | DEV_COMPUTE_CLUSTER0_C71SS1_0_PLL_CTRL_CLK | CLK_STATE_READY | 500000000 | |-------------------------------------------------------------------------------------------------------|

以下是 如何更改 A72内核的速度等级"H"的时钟 (即、2GHz 至1.2GHz)

diff --git a/packages/ti/boot/sbl/soc/k3/sbl_soc_cfg.h b/packages/ti/boot/sbl/soc/k3/sbl_soc_cfg.h index 53800ea..01e2f26 100755 --- a/packages/ti/boot/sbl/soc/k3/sbl_soc_cfg.h +++ b/packages/ti/boot/sbl/soc/k3/sbl_soc_cfg.h @@ -653,12 +653,12 @@ extern uint16_t sblMapOtpVidToMilliVolts[256]; #define SBL_PROC_ID_MPU1_CPU0 (SCICLIENT_PROC_ID_A72SS0_CORE0) #define SBL_DEV_ID_MPU1_CPU0 (TISCI_DEV_A72SS0_CORE0) #define SBL_CLK_ID_MPU1_CPU0 (TISCI_DEV_A72SS0_CORE0_ARM_CLK_CLK) -#define SBL_MPU1_CPU0_FREQ_HZ (2000000000) +#define SBL_MPU1_CPU0_FREQ_HZ (1200000000) #define SBL_PROC_ID_MPU1_CPU1 (SCICLIENT_PROC_ID_A72SS0_CORE1) #define SBL_DEV_ID_MPU1_CPU1 (TISCI_DEV_A72SS0_CORE1) #define SBL_CLK_ID_MPU1_CPU1 (TISCI_DEV_A72SS0_CORE1_ARM_CLK_CLK) -#define SBL_MPU1_CPU1_FREQ_HZ (2000000000) +#define SBL_MPU1_CPU1_FREQ_HZ (1200000000)

所需构建

Assuming the SOC is J721s2 (SDK 8.6), Default SBL with MMCSD boot media

For custom SBL and different boot media, please adapt the build commands accordingly

cd ${PSDKRA}/pdk_j721s2_08_06_00_31/packages/ti/build/

make sbl_lib_mmcsd_hlos_clean BOARD=j721s2_evm

make sbl_mmcsd_img_hlos_clean BOARD=j721s2_evm

make sbl_lib_mmcsd_hlos BOARD=j721s2_evm

make sbl_mmcsd_img_hlos BOARD=j721s2_evm

验证 命令:

k3conf dump clock 202 k3conf dump clock 203

输出:

root@j721s2-evm:~# k3conf dump clock 202 |--------------------------------------------------------------------------------| | VERSION INFO | |--------------------------------------------------------------------------------| | K3CONF | (version v0.1-88-g982f5c2 built Wed Mar 1 18:42:41 UTC 2023) | | SoC | J721S2 SR1.0 | | SYSFW | ABI: 3.1 (firmware version 0x0008 '8.6.3--v08.06.03 (Chill Capybar)') | |--------------------------------------------------------------------------------| |-----------------------------------------------------------------------------------------| | Device ID | Clock ID | Clock Name | Status | Clock Frequency | |-----------------------------------------------------------------------------------------| | 202 | 0 | DEV_A72SS0_CORE0_ARM_CLK_CLK | CLK_STATE_READY | 1200000000 | |-----------------------------------------------------------------------------------------| root@j721s2-evm:~# k3conf dump clock 203 |--------------------------------------------------------------------------------| | VERSION INFO | |--------------------------------------------------------------------------------| | K3CONF | (version v0.1-88-g982f5c2 built Wed Mar 1 18:42:41 UTC 2023) | | SoC | J721S2 SR1.0 | | SYSFW | ABI: 3.1 (firmware version 0x0008 '8.6.3--v08.06.03 (Chill Capybar)') | |--------------------------------------------------------------------------------| |-----------------------------------------------------------------------------------------| | Device ID | Clock ID | Clock Name | Status | Clock Frequency | |-----------------------------------------------------------------------------------------| | 203 | 0 | DEV_A72SS0_CORE1_ARM_CLK_CLK | CLK_STATE_READY | 1200000000 | |-----------------------------------------------------------------------------------------|

根据速度等级和功耗优化的组合、可以对其他内核/HWA 执行类似的操作。

3. 禁用/移除其他内核

TDA4AL88和 TDA4VL21等子集是 四核 R5器件、而其超集则是六核器件。 还有其他只有1个 C7x 内核的子集。

在 u-boot、Linux 和 vision_apps 中需要对相同的内容进行更改。

例如、可以按如下所示删除 MCU3_0 (或) main_r5fs1

diff --git a/arch/arm/dts/k3-j721s2-common-proc-board.dts b/arch/arm/dts/k3-j721s2-common-proc-board.dts

index 5b7e33490f..ffd9c8568b 100644

--- a/arch/arm/dts/k3-j721s2-common-proc-board.dts

+++ b/arch/arm/dts/k3-j721s2-common-proc-board.dts

@@ -32,8 +32,6 @@

remoteproc1 = &mcu_r5fss0_core1;

remoteproc2 = &main_r5fss0_core0;

remoteproc3 = &main_r5fss0_core1;

- remoteproc4 = &main_r5fss1_core0;

- remoteproc5 = &main_r5fss1_core1;

remoteproc6 = &c71_0;

remoteproc7 = &c71_1;

};

diff --git a/arch/arm/dts/k3-j721s2-main.dtsi b/arch/arm/dts/k3-j721s2-main.dtsi

index 18e5113336..d9bf23b1e9 100644

--- a/arch/arm/dts/k3-j721s2-main.dtsi

+++ b/arch/arm/dts/k3-j721s2-main.dtsi

@@ -1152,46 +1152,6 @@

};

};

- main_r5fss1: r5fss@5e00000 {

- compatible = "ti,j721s2-r5fss";

- ti,cluster-mode = <0>;

- #address-cells = <1>;

- #size-cells = <1>;

- ranges = <0x5e00000 0x00 0x5e00000 0x20000>,

- <0x5f00000 0x00 0x5f00000 0x20000>;

- power-domains = <&k3_pds 278 TI_SCI_PD_EXCLUSIVE>;

-

- main_r5fss1_core0: r5f@5e00000 {

- compatible = "ti,j721s2-r5f";

- reg = <0x5e00000 0x00010000>,

- <0x5e10000 0x00010000>;

- reg-names = "atcm", "btcm";

- ti,sci = <&sms>;

- ti,sci-dev-id = <281>;

- ti,sci-proc-ids = <0x08 0xff>;

- resets = <&k3_reset 281 1>;

- firmware-name = "j721s2-main-r5f1_0-fw";

- ti,atcm-enable = <1>;

- ti,btcm-enable = <1>;

- ti,loczrama = <1>;

- };

-

- main_r5fss1_core1: r5f@5f00000 {

- compatible = "ti,j721s2-r5f";

- reg = <0x5f00000 0x00010000>,

- <0x5f10000 0x00010000>;

- reg-names = "atcm", "btcm";

- ti,sci = <&sms>;

- ti,sci-dev-id = <282>;

- ti,sci-proc-ids = <0x09 0xff>;

- resets = <&k3_reset 282 1>;

- firmware-name = "j721s2-main-r5f1_1-fw";

- ti,atcm-enable = <1>;

- ti,btcm-enable = <1>;

- ti,loczrama = <1>;

- };

- };

-

c71_0: dsp@64800000 {

compatible = "ti,j721s2-c71-dsp";

reg = <0x00 0x64800000 0x00 0x00080000>,

diff --git a/arch/arm/dts/k3-j721s2-som-p0.dtsi b/arch/arm/dts/k3-j721s2-som-p0.dtsi

index f3080e948e..c4df1d51bd 100644

--- a/arch/arm/dts/k3-j721s2-som-p0.dtsi

+++ b/arch/arm/dts/k3-j721s2-som-p0.dtsi

@@ -78,30 +78,6 @@

no-map;

};

- main_r5fss1_core0_dma_memory_region: r5f-dma-memory@a4000000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa4000000 0x00 0x100000>;

- no-map;

- };

-

- main_r5fss1_core0_memory_region: r5f-memory@a4100000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa4100000 0x00 0xf00000>;

- no-map;

- };

-

- main_r5fss1_core1_dma_memory_region: r5f-dma-memory@a5000000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa5000000 0x00 0x100000>;

- no-map;

- };

-

- main_r5fss1_core1_memory_region: r5f-memory@a5100000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa5100000 0x00 0xf00000>;

- no-map;

- };

-

c71_0_dma_memory_region: c71-dma-memory@a6000000 {

compatible = "shared-dma-pool";

reg = <0x00 0xa6000000 0x00 0x100000>;

@@ -251,17 +227,7 @@

};

&mailbox0_cluster2 {

- interrupts = <428>;

-

- mbox_main_r5fss1_core0: mbox-main-r5fss1-core0 {

- ti,mbox-rx = <0 0 0>;

- ti,mbox-tx = <1 0 0>;

- };

-

- mbox_main_r5fss1_core1: mbox-main-r5fss1-core1 {

- ti,mbox-rx = <2 0 0>;

- ti,mbox-tx = <3 0 0>;

- };

+ status = "disabled";

};

&mailbox0_cluster3 {

@@ -382,18 +348,6 @@

<&main_r5fss0_core1_memory_region>;

};

-&main_r5fss1_core0 {

- mboxes = <&mailbox0_cluster2 &mbox_main_r5fss1_core0>;

- memory-region = <&main_r5fss1_core0_dma_memory_region>,

- <&main_r5fss1_core0_memory_region>;

-};

-

-&main_r5fss1_core1 {

- mboxes = <&mailbox0_cluster2 &mbox_main_r5fss1_core1>;

- memory-region = <&main_r5fss1_core1_dma_memory_region>,

- <&main_r5fss1_core1_memory_region>;

-};

-

&c71_0 {

mboxes = <&mailbox0_cluster4 &mbox_c71_0>;

memory-region = <&c71_0_dma_memory_region>,

diff --git a/platform/j721s2/rtos/app_mem_map.h b/platform/j721s2/rtos/app_mem_map.h

index 4f1c7f6..e562580 100755

--- a/platform/j721s2/rtos/app_mem_map.h

+++ b/platform/j721s2/rtos/app_mem_map.h

@@ -127,22 +127,6 @@

#define DDR_MCU2_1_DTS_ADDR (0xA4100000u)

#define DDR_MCU2_1_DTS_SIZE (0x01F00000u)

-/* DDR for MCU3_0 for Linux IPC [ size 1024.00 KB ] */

-#define DDR_MCU3_0_IPC_ADDR (0xA6000000u)

-#define DDR_MCU3_0_IPC_SIZE (0x00100000u)

-

-/* DDR for MCU3_0 for all sections, used for reserving memory in DTS file [ size 15.00 MB ] */

-#define DDR_MCU3_0_DTS_ADDR (0xA6100000u)

-#define DDR_MCU3_0_DTS_SIZE (0x00F00000u)

-

-/* DDR for MCU3_1 for Linux IPC [ size 1024.00 KB ] */

-#define DDR_MCU3_1_IPC_ADDR (0xA7000000u)

-#define DDR_MCU3_1_IPC_SIZE (0x00100000u)

-

-/* DDR for MCU3_1 for all sections, used for reserving memory in DTS file [ size 15.00 MB ] */

-#define DDR_MCU3_1_DTS_ADDR (0xA7100000u)

-#define DDR_MCU3_1_DTS_SIZE (0x00F00000u)

-

/* Memory for IPC Vring's. MUST be non-cached or cache-coherent [ size 32.00 MB ] */

#define IPC_VRING_MEM_ADDR (0xA8000000u)

#define IPC_VRING_MEM_SIZE (0x02000000u)

@@ -195,14 +179,6 @@

#define DDR_MCU2_1_LOCAL_HEAP_ADDR (0xDA000000u)

#define DDR_MCU2_1_LOCAL_HEAP_SIZE (0x01000000u)

-/* DDR for MCU3_0 for local heap [ size 8.00 MB ] */

-#define DDR_MCU3_0_LOCAL_HEAP_ADDR (0xDB000000u)

-#define DDR_MCU3_0_LOCAL_HEAP_SIZE (0x00800000u)

-

-/* DDR for MCU3_1 for local heap [ size 8.00 MB ] */

-#define DDR_MCU3_1_LOCAL_HEAP_ADDR (0xDB800000u)

-#define DDR_MCU3_1_LOCAL_HEAP_SIZE (0x00800000u)

-

/* DDR for c7x_1 for Scratch Memory [ size 368.00 MB ] */

#define DDR_C7X_1_SCRATCH_ADDR (0x100000000u)

#define DDR_C7X_1_SCRATCH_SIZE (0x17000000u)

diff --git a/platform/j721s2/rtos/gen_linker_mem_map.py b/platform/j721s2/rtos/gen_linker_mem_map.py

index 56725bc..c19fd69 100755

--- a/platform/j721s2/rtos/gen_linker_mem_map.py

+++ b/platform/j721s2/rtos/gen_linker_mem_map.py

@@ -79,7 +79,7 @@

# This will generate linker command file at below folders

# ./<cpu name>/linker_mem_map.cmd

#

-# Here CPU name is mpu1, c7x_1, c7x_2, mcu1_0, mcu2_0, mcu3_0

+# Here CPU name is mpu1, c7x_1, c7x_2, mcu1_0, mcu2_0

#

#

from ti_psdk_rtos_tools import *

@@ -193,16 +193,6 @@ mcu2_1_ddr_resource_table_addr = mcu2_1_ddr_ipc_addr + linux_ddr_ipc_size;

mcu2_1_ddr_addr = mcu2_1_ddr_resource_table_addr + linux_ddr_resource_table_size;

mcu2_1_ddr_size = 32*MB - (mcu2_1_ddr_addr-mcu2_1_ddr_ipc_addr);

-mcu3_0_ddr_ipc_addr = mcu2_1_ddr_addr + mcu2_1_ddr_size;

-mcu3_0_ddr_resource_table_addr = mcu3_0_ddr_ipc_addr + linux_ddr_ipc_size;

-mcu3_0_ddr_addr = mcu3_0_ddr_resource_table_addr + linux_ddr_resource_table_size;

-mcu3_0_ddr_size = 16*MB - (mcu3_0_ddr_addr-mcu3_0_ddr_ipc_addr);

-

-mcu3_1_ddr_ipc_addr = mcu3_0_ddr_addr + mcu3_0_ddr_size;

-mcu3_1_ddr_resource_table_addr = mcu3_1_ddr_ipc_addr + linux_ddr_ipc_size;

-mcu3_1_ddr_addr = mcu3_1_ddr_resource_table_addr + linux_ddr_resource_table_size;

-mcu3_1_ddr_size = 16*MB - (mcu3_1_ddr_addr-mcu3_1_ddr_ipc_addr);

-

#

# DDR memory allocation for various shared memories

#

@@ -253,10 +243,6 @@ mcu2_0_ddr_local_heap_addr = mcu1_1_ddr_local_heap_addr + mcu1_1_ddr_local_heap

mcu2_0_ddr_local_heap_size = 16*MB;

mcu2_1_ddr_local_heap_addr = mcu2_0_ddr_local_heap_addr + mcu2_0_ddr_local_heap_size;

mcu2_1_ddr_local_heap_size = 16*MB;

-mcu3_0_ddr_local_heap_addr = mcu2_1_ddr_local_heap_addr + mcu2_1_ddr_local_heap_size;

-mcu3_0_ddr_local_heap_size = 8*MB;

-mcu3_1_ddr_local_heap_addr = mcu3_0_ddr_local_heap_addr + mcu3_0_ddr_local_heap_size;

-mcu3_1_ddr_local_heap_size = 8*MB;

c7x_1_ddr_scratch_addr = ddr_mem_addr_hi;

c7x_1_ddr_scratch_size = 368*MB;

@@ -343,26 +329,6 @@ mcu2_1_ddr_total.concat(mcu2_1_ddr_resource_table);

mcu2_1_ddr_total.concat(mcu2_1_ddr);

mcu2_1_ddr_total.setDtsName("vision_apps_main_r5fss0_core1_memory_region", "vision-apps-r5f-memory");

-mcu3_0_ddr_ipc = MemSection("DDR_MCU3_0_IPC", "RWIX", mcu3_0_ddr_ipc_addr, linux_ddr_ipc_size, "DDR for MCU3_0 for Linux IPC");

-mcu3_0_ddr_ipc.setDtsName("vision_apps_main_r5fss1_core0_dma_memory_region", "vision-apps-r5f-dma-memory");

-mcu3_0_ddr_resource_table = MemSection("DDR_MCU3_0_RESOURCE_TABLE", "RWIX", mcu3_0_ddr_resource_table_addr, linux_ddr_resource_table_size, "DDR for MCU3_0 for Linux resource table");

-mcu3_0_ddr = MemSection("DDR_MCU3_0", "RWIX", mcu3_0_ddr_addr, mcu3_0_ddr_size, "DDR for MCU3_0 for code/data");

-mcu3_0_ddr_local_heap = MemSection("DDR_MCU3_0_LOCAL_HEAP", "RWIX", mcu3_0_ddr_local_heap_addr, mcu3_0_ddr_local_heap_size, "DDR for MCU3_0 for local heap");

-mcu3_0_ddr_total = MemSection("DDR_MCU3_0_DTS", "", 0, 0, "DDR for MCU3_0 for all sections, used for reserving memory in DTS file");

-mcu3_0_ddr_total.concat(mcu3_0_ddr_resource_table);

-mcu3_0_ddr_total.concat(mcu3_0_ddr);

-mcu3_0_ddr_total.setDtsName("vision_apps_main_r5fss1_core0_memory_region", "vision-apps-r5f-memory");

-

-mcu3_1_ddr_ipc = MemSection("DDR_MCU3_1_IPC", "RWIX", mcu3_1_ddr_ipc_addr, linux_ddr_ipc_size, "DDR for MCU3_1 for Linux IPC");

-mcu3_1_ddr_ipc.setDtsName("vision_apps_main_r5fss1_core1_dma_memory_region", "vision-apps-r5f-dma-memory");

-mcu3_1_ddr_resource_table = MemSection("DDR_MCU3_1_RESOURCE_TABLE", "RWIX", mcu3_1_ddr_resource_table_addr, linux_ddr_resource_table_size, "DDR for MCU3_1 for Linux resource table");

-mcu3_1_ddr = MemSection("DDR_MCU3_1", "RWIX", mcu3_1_ddr_addr, mcu3_1_ddr_size, "DDR for MCU3_1 for code/data");

-mcu3_1_ddr_local_heap = MemSection("DDR_MCU3_1_LOCAL_HEAP", "RWIX", mcu3_1_ddr_local_heap_addr, mcu3_1_ddr_local_heap_size, "DDR for MCU3_1 for local heap");

-mcu3_1_ddr_total = MemSection("DDR_MCU3_1_DTS", "", 0, 0, "DDR for MCU3_1 for all sections, used for reserving memory in DTS file");

-mcu3_1_ddr_total.concat(mcu3_1_ddr_resource_table);

-mcu3_1_ddr_total.concat(mcu3_1_ddr);

-mcu3_1_ddr_total.setDtsName("vision_apps_main_r5fss1_core1_memory_region", "vision-apps-r5f-memory");

-

c7x_2_ddr_ipc = MemSection("DDR_C7x_2_IPC", "RWIX", c7x_2_ddr_ipc_addr, linux_ddr_ipc_size, "DDR for C7x_2 for Linux IPC");

c7x_2_ddr_ipc.setDtsName("vision_apps_c71_1_dma_memory_region", "vision-apps-c71_1-dma-memory");

c7x_2_ddr_resource_table = MemSection("DDR_C7x_2_RESOURCE_TABLE", "RWIX", c7x_2_ddr_resource_table_addr, linux_ddr_resource_table_size, "DDR for C7x_2 for Linux resource table");

@@ -422,8 +388,6 @@ vision_apps_core_heaps_lo = MemSection("DDR_VISION_APPS_CORE_HEAPS_LO_DTS", "",

vision_apps_core_heaps_lo.concat(mcu1_0_ddr_local_heap);

vision_apps_core_heaps_lo.concat(mcu2_0_ddr_local_heap);

vision_apps_core_heaps_lo.concat(mcu2_1_ddr_local_heap);

-vision_apps_core_heaps_lo.concat(mcu3_0_ddr_local_heap);

-vision_apps_core_heaps_lo.concat(mcu3_1_ddr_local_heap);

vision_apps_core_heaps_lo.setDtsName("vision_apps_core_heaps_lo", "vision-apps-core-heap-memory-lo");

c7x_1_ddr_local_heap_phy = MemSection("DDR_C7X_1_LOCAL_HEAP", "RWIX", ddr_mem_addr_hi_phy, (c7x_1_ddr_scratch_size + c7x_1_ddr_local_heap_size + c7x_2_ddr_scratch_size + c7x_2_ddr_local_heap_size), "DDR for c7x_1, c7x_2 for scratch memory and local heap");

@@ -498,34 +462,6 @@ mcu2_1_mmap.addMemSection( ddr_shared_mem );

mcu2_1_mmap.addMemSection( mcu2_1_main_ocram );

mcu2_1_mmap.checkOverlap();

-mcu3_0_mmap = MemoryMap("mcu3_0");

-mcu3_0_mmap.addMemSection( mcu_r5f_tcma_vecs );

-mcu3_0_mmap.addMemSection( mcu_r5f_tcma );

-mcu3_0_mmap.addMemSection( r5f_tcmb0 );

-mcu3_0_mmap.addMemSection( mcu3_0_ddr_ipc );

-mcu3_0_mmap.addMemSection( mcu3_0_ddr_resource_table );

-mcu3_0_mmap.addMemSection( mcu3_0_ddr );

-mcu3_0_mmap.addMemSection( app_log_mem );

-mcu3_0_mmap.addMemSection( tiovx_obj_desc_mem );

-mcu3_0_mmap.addMemSection( ipc_vring_mem );

-mcu3_0_mmap.addMemSection( mcu3_0_ddr_local_heap );

-mcu3_0_mmap.addMemSection( ddr_shared_mem );

-mcu3_0_mmap.checkOverlap();

-

-mcu3_1_mmap = MemoryMap("mcu3_1");

-mcu3_1_mmap.addMemSection( mcu_r5f_tcma_vecs );

-mcu3_1_mmap.addMemSection( mcu_r5f_tcma );

-mcu3_1_mmap.addMemSection( r5f_tcmb0 );

-mcu3_1_mmap.addMemSection( mcu3_1_ddr_ipc );

-mcu3_1_mmap.addMemSection( mcu3_1_ddr_resource_table );

-mcu3_1_mmap.addMemSection( mcu3_1_ddr );

-mcu3_1_mmap.addMemSection( app_log_mem );

-mcu3_1_mmap.addMemSection( tiovx_obj_desc_mem );

-mcu3_1_mmap.addMemSection( ipc_vring_mem );

-mcu3_1_mmap.addMemSection( mcu3_1_ddr_local_heap );

-mcu3_1_mmap.addMemSection( ddr_shared_mem );

-mcu3_1_mmap.checkOverlap();

-

c7x_1_mmap = MemoryMap("c7x_1");

c7x_1_mmap.addMemSection( c7x_1_l2 );

c7x_1_mmap.addMemSection( c7x_1_l1 );

@@ -585,14 +521,6 @@ html_mmap.addMemSection( mcu2_1_ddr_ipc );

html_mmap.addMemSection( mcu2_1_ddr_resource_table );

html_mmap.addMemSection( mcu2_1_ddr );

html_mmap.addMemSection( mcu2_1_ddr_local_heap );

-html_mmap.addMemSection( mcu3_0_ddr_ipc );

-html_mmap.addMemSection( mcu3_0_ddr_resource_table );

-html_mmap.addMemSection( mcu3_0_ddr );

-html_mmap.addMemSection( mcu3_0_ddr_local_heap );

-html_mmap.addMemSection( mcu3_1_ddr_ipc );

-html_mmap.addMemSection( mcu3_1_ddr_resource_table );

-html_mmap.addMemSection( mcu3_1_ddr );

-html_mmap.addMemSection( mcu3_1_ddr_local_heap );

html_mmap.addMemSection( c7x_1_ddr_ipc );

html_mmap.addMemSection( c7x_1_ddr_resource_table );

html_mmap.addMemSection( c7x_1_ddr_boot );

@@ -628,16 +556,12 @@ c_header_mmap.addMemSection( mcu1_0_ddr_ipc );

c_header_mmap.addMemSection( mcu1_1_ddr_ipc );

c_header_mmap.addMemSection( mcu2_0_ddr_ipc );

c_header_mmap.addMemSection( mcu2_1_ddr_ipc );

-c_header_mmap.addMemSection( mcu3_0_ddr_ipc );

-c_header_mmap.addMemSection( mcu3_1_ddr_ipc );

c_header_mmap.addMemSection( c7x_1_ddr_ipc );

c_header_mmap.addMemSection( c7x_2_ddr_ipc );

c_header_mmap.addMemSection( mcu1_0_ddr_total );

c_header_mmap.addMemSection( mcu1_1_ddr_total );

c_header_mmap.addMemSection( mcu2_0_ddr_total );

c_header_mmap.addMemSection( mcu2_1_ddr_total );

-c_header_mmap.addMemSection( mcu3_0_ddr_total );

-c_header_mmap.addMemSection( mcu3_1_ddr_total );

c_header_mmap.addMemSection( c7x_1_ddr_total );

c_header_mmap.addMemSection( c7x_2_ddr_total );

@@ -645,8 +569,6 @@ c_header_mmap.addMemSection( mcu1_0_ddr_local_heap);

c_header_mmap.addMemSection( mcu1_1_ddr_local_heap);

c_header_mmap.addMemSection( mcu2_0_ddr_local_heap);

c_header_mmap.addMemSection( mcu2_1_ddr_local_heap);

-c_header_mmap.addMemSection( mcu3_0_ddr_local_heap);

-c_header_mmap.addMemSection( mcu3_1_ddr_local_heap);

c_header_mmap.addMemSection( c7x_1_ddr_local_heap);

c_header_mmap.addMemSection( c7x_1_ddr_scratch);

c_header_mmap.addMemSection( c7x_2_ddr_local_heap);

@@ -672,10 +594,6 @@ dts_mmap.addMemSection( mcu2_0_ddr_ipc );

dts_mmap.addMemSection( mcu2_0_ddr_total );

dts_mmap.addMemSection( mcu2_1_ddr_ipc );

dts_mmap.addMemSection( mcu2_1_ddr_total );

-dts_mmap.addMemSection( mcu3_0_ddr_ipc );

-dts_mmap.addMemSection( mcu3_0_ddr_total );

-dts_mmap.addMemSection( mcu3_1_ddr_ipc );

-dts_mmap.addMemSection( mcu3_1_ddr_total );

dts_mmap.addMemSection( c7x_1_ddr_ipc );

dts_mmap.addMemSection( c7x_1_ddr_total );

dts_mmap.addMemSection( c7x_2_ddr_ipc );

@@ -696,8 +614,6 @@ LinkerCmdFile(mcu1_0_mmap, "./mcu1_0/linker_mem_map.cmd").export();

LinkerCmdFile(mcu1_1_mmap, "./mcu1_1/linker_mem_map.cmd").export();

LinkerCmdFile(mcu2_0_mmap, "./mcu2_0/linker_mem_map.cmd").export();

LinkerCmdFile(mcu2_1_mmap, "./mcu2_1/linker_mem_map.cmd").export();

-LinkerCmdFile(mcu3_0_mmap, "./mcu3_0/linker_mem_map.cmd").export();

-LinkerCmdFile(mcu3_1_mmap, "./mcu3_1/linker_mem_map.cmd").export();

HtmlMmapTable(html_mmap, "./system_memory_map.html").export();

diff --git a/platform/j721s2/rtos/k3-j721s2-rtos-memory-map.dtsi b/platform/j721s2/rtos/k3-j721s2-rtos-memory-map.dtsi

index 86855a6..214590f 100644

--- a/platform/j721s2/rtos/k3-j721s2-rtos-memory-map.dtsi

+++ b/platform/j721s2/rtos/k3-j721s2-rtos-memory-map.dtsi

@@ -4,7 +4,7 @@

* IMPORTANT NOTE: Follow below instructions to apply the updated memory map to linux dtsi file,

*

* 1. Copy the memory sections, from the generated dts file, to the file shown below under reserved_memory: reserved-memory { ... }

- * ${LINUX_KERNEL_PATH}/arch/arm64/boot/dts/ti/k3-j721s2-rtos-memory-map.dtsi

+ * ${LINUX_KERNEL_PATH}/arch/arm64/boot/dts/ti/k3-j721e-rtos-memory-map.dtsi

*

* 2. Rebuild the dtb, dtbo from PSDK Linux install directory

* make linux-dtbs

@@ -55,26 +55,6 @@

reg = <0x00 0xa4100000 0x00 0x01f00000>;

no-map;

};

- vision_apps_main_r5fss1_core0_dma_memory_region: vision-apps-r5f-dma-memory@a6000000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa6000000 0x00 0x00100000>;

- no-map;

- };

- vision_apps_main_r5fss1_core0_memory_region: vision-apps-r5f-memory@a6100000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa6100000 0x00 0x00f00000>;

- no-map;

- };

- vision_apps_main_r5fss1_core1_dma_memory_region: vision-apps-r5f-dma-memory@a7000000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa7000000 0x00 0x00100000>;

- no-map;

- };

- vision_apps_main_r5fss1_core1_memory_region: vision-apps-r5f-memory@a7100000 {

- compatible = "shared-dma-pool";

- reg = <0x00 0xa7100000 0x00 0x00f00000>;

- no-map;

- };

vision_apps_rtos_ipc_memory_region: vision-apps-rtos-ipc-memory-region@a8000000 {

compatible = "shared-dma-pool";

reg = <0x00 0xa8000000 0x00 0x02000000>;

@@ -111,7 +91,7 @@

};

vision_apps_core_heaps_lo: vision-apps-core-heap-memory-lo@d8000000 {

compatible = "shared-dma-pool";

- reg = <0x00 0xd8000000 0x00 0x04000000>;

+ reg = <0x00 0xd8000000 0x00 0x03000000>;

no-map;

};

vision_apps_core_heaps_hi: vision-apps-core-heap-memory-hi@880000000 {

diff --git a/platform/j721s2/rtos/system_memory_map.html b/platform/j721s2/rtos/system_memory_map.html

index 1859f9b..57d49f5 100644

--- a/platform/j721s2/rtos/system_memory_map.html

+++ b/platform/j721s2/rtos/system_memory_map.html

@@ -192,54 +192,6 @@

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU2_1 for code/data</td>

</tr>

- <tr>

- <td class="tg-6sgx">DDR_MCU3_0_IPC</td>

- <td class="tg-6sgx">0xA6000000</td>

- <td class="tg-6sgx">0xA60FFFFF</td>

- <td class="tg-6sgx">1024.00 KB</td>

- <td class="tg-6sgx">RWIX</td>

- <td class="tg-6sgx">DDR for MCU3_0 for Linux IPC</td>

- </tr>

- <tr>

- <td class="tg-kftd">DDR_MCU3_0_RESOURCE_TABLE</td>

- <td class="tg-kftd">0xA6100000</td>

- <td class="tg-kftd">0xA61003FF</td>

- <td class="tg-kftd">1024 B</td>

- <td class="tg-kftd">RWIX</td>

- <td class="tg-kftd">DDR for MCU3_0 for Linux resource table</td>

- </tr>

- <tr>

- <td class="tg-6sgx">DDR_MCU3_0</td>

- <td class="tg-6sgx">0xA6100400</td>

- <td class="tg-6sgx">0xA6FFFFFF</td>

- <td class="tg-6sgx">15.00 MB</td>

- <td class="tg-6sgx">RWIX</td>

- <td class="tg-6sgx">DDR for MCU3_0 for code/data</td>

- </tr>

- <tr>

- <td class="tg-kftd">DDR_MCU3_1_IPC</td>

- <td class="tg-kftd">0xA7000000</td>

- <td class="tg-kftd">0xA70FFFFF</td>

- <td class="tg-kftd">1024.00 KB</td>

- <td class="tg-kftd">RWIX</td>

- <td class="tg-kftd">DDR for MCU3_1 for Linux IPC</td>

- </tr>

- <tr>

- <td class="tg-6sgx">DDR_MCU3_1_RESOURCE_TABLE</td>

- <td class="tg-6sgx">0xA7100000</td>

- <td class="tg-6sgx">0xA71003FF</td>

- <td class="tg-6sgx">1024 B</td>

- <td class="tg-6sgx">RWIX</td>

- <td class="tg-6sgx">DDR for MCU3_1 for Linux resource table</td>

- </tr>

- <tr>

- <td class="tg-kftd">DDR_MCU3_1</td>

- <td class="tg-kftd">0xA7100400</td>

- <td class="tg-kftd">0xA7FFFFFF</td>

- <td class="tg-kftd">15.00 MB</td>

- <td class="tg-kftd">RWIX</td>

- <td class="tg-kftd">DDR for MCU3_1 for code/data</td>

- </tr>

<tr>

<td class="tg-6sgx">IPC_VRING_MEM</td>

<td class="tg-6sgx">0xA8000000</td>

@@ -408,22 +360,6 @@

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU2_1 for local heap</td>

</tr>

- <tr>

- <td class="tg-kftd">DDR_MCU3_0_LOCAL_HEAP</td>

- <td class="tg-kftd">0xDB000000</td>

- <td class="tg-kftd">0xDB7FFFFF</td>

- <td class="tg-kftd"> 8.00 MB</td>

- <td class="tg-kftd">RWIX</td>

- <td class="tg-kftd">DDR for MCU3_0 for local heap</td>

- </tr>

- <tr>

- <td class="tg-6sgx">DDR_MCU3_1_LOCAL_HEAP</td>

- <td class="tg-6sgx">0xDB800000</td>

- <td class="tg-6sgx">0xDBFFFFFF</td>

- <td class="tg-6sgx"> 8.00 MB</td>

- <td class="tg-6sgx">RWIX</td>

- <td class="tg-6sgx">DDR for MCU3_1 for local heap</td>

- </tr>

<tr>

<td class="tg-kftd">DDR_C7X_1_SCRATCH</td>

<td class="tg-kftd">0x100000000</td>

所需构建

cd ${PSDKLA}/

make linux-dtbs

Assuming SOC as J721s2 (SDK 8.6)

To Build vision_apps

=====================

cd ${PSDKRA}/vision_apps

make vision_apps_scrub

make vision_apps

To Build combined_app image

============================

cd ${PSDKRA}/pdk_j721s2_08_06_00_31/packages/ti/boot/sbl/tools/combined_appimage/

make clean BOARD=j721s2_evm

make BOARD=j721s2_evm HLOS_BOOT=optimized

验证 命令:

cat /proc/interrupts

输出:

在命令输入端看不到 main-r5fs1-core0中断

4. 删除 驱动程序为禁用的 IP (GPU,EDP,CSITX 等)

子集器件需要删除一些硬件 IP。

例如:

a) 子集分析设备如 TDA4AL、GPU 不可用。 因此、为了从 SDK 中删除 GPU 支持、需要在 u-boot 和 Linux 内核上进行更改、如下所示。

diff --git a/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi b/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

index 69216fe05..8ee1a470e 100644

--- a/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

@@ -288,16 +288,6 @@

power-domains = <&k3_pds 358 TI_SCI_PD_EXCLUSIVE>;

};

- gpu: gpu@4e20000000 {

- compatible = "ti,j721s2-pvr", "img,pvr-bxs64";

- reg = <0x4e 0x20000000 0x00 0x80000>;

- interrupts = <GIC_SPI 24 IRQ_TYPE_LEVEL_HIGH>;

- power-domains = <&k3_pds 130 TI_SCI_PD_EXCLUSIVE>,

- <&k3_pds 373 TI_SCI_PD_EXCLUSIVE>;

- power-domain-names = "gpu_0", "gpucore_0";

- clocks = <&k3_clks 130 1>;

- };

-

main_gpio0: gpio@600000 {

compatible = "ti,j721e-gpio", "ti,keystone-gpio";

reg = <0x00 0x00600000 0x00 0x100>;

diff --git a/arch/arm64/boot/dts/ti/k3-j721s2.dtsi b/arch/arm64/boot/dts/ti/k3-j721s2.dtsi

index 75bc8dfac..dd2f0ebc8 100644

--- a/arch/arm64/boot/dts/ti/k3-j721s2.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-j721s2.dtsi

@@ -122,7 +122,6 @@

<0x00 0x70000000 0x00 0x70000000 0x00 0x00400000>, /* MSMC RAM */

<0x00 0x30000000 0x00 0x30000000 0x00 0x0c400000>, /* MAIN NAVSS */

<0x41 0x00000000 0x41 0x00000000 0x01 0x00000000>, /* PCIe1 DAT1 */

- <0x4e 0x20000000 0x4e 0x20000000 0x00 0x00080000>, /* GPU */

/* MCUSS_WKUP Range */

<0x00 0x28380000 0x00 0x28380000 0x00 0x03880000>,

所需构建

cd ${PSDKLA}/

make linux-dtbs

Assuming SOC as J721s2 (SDK 8.6)

cd ${PSDKRA}/pdk_j721s2_08_06_00_31/packages/ti/boot/sbl/tools/combined_appimage/

make clean BOARD=j721s2_evm

make BOARD=j721s2_evm HLOS_BOOT=optimized

验证 命令:

devmem2 0x4E20000018

输出:

内核崩溃

b) 对于 TDA4AL88等一些子集分析器件、EDP 不支持。 因此、为了 从 SDK 中删除 EDP 支持、需要在 Linux 内核上进行更改、如下所示。

diff --git a/arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dts b/arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dts

index b6158a27f..a8ad37a9a 100644

--- a/arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dts

+++ b/arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dts

@@ -148,19 +148,6 @@

regulator-always-on;

};

- dp0: dp0-connector {

- compatible = "dp-connector";

- label = "DP0";

- type = "full-size";

- dp-pwr-supply = <&dp0_pwr_3v3>;

-

- port {

- dp0_connector_in: endpoint {

- remote-endpoint = <&dp0_out>;

- };

- };

- };

-

panel {

compatible = "ti,panel-edp";

power-supply = <&dp1_pwr_3v3>;

@@ -626,13 +613,6 @@

#address-cells = <1>;

#size-cells = <0>;

- port@0 {

- reg = <0>;

- dpi0_out: endpoint {

- remote-endpoint = <&dp0_in>;

- };

- };

-

port@2 {

reg = <2>;

dpi2_out: endpoint {

@@ -673,31 +653,6 @@

};

};

-&mhdp {

- pinctrl-names = "default";

- pinctrl-0 = <&dp0_pins_default>;

- cdns,no-hpd;

-};

-

-&dp0_ports {

- #address-cells = <1>;

- #size-cells = <0>;

-

- port@0 {

- reg = <0>;

- dp0_in: endpoint {

- remote-endpoint = <&dpi0_out>;

- };

- };

-

- port@4 {

- reg = <4>;

- dp0_out: endpoint {

- remote-endpoint = <&dp0_connector_in>;

- };

- };

-};

-

&main_mcan0 {

status = "disabled";

};

diff --git a/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi b/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

index 69216fe05..8ee1a470e 100644

--- a/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

@@ -1493,32 +1443,6 @@

power-domains = <&k3_pds 346 TI_SCI_PD_EXCLUSIVE>;

};

- mhdp: dp-bridge@a000000 {

- compatible = "ti,j721e-mhdp8546";

- /*

- * Note: we do not map DPTX PHY area, as that is handled by

- * the PHY driver.

- */

- reg = <0x0 0xa000000 0x0 0x30a00>, /* DSS_EDP0_V2A_CORE_VP_REGS_APB */

- <0x0 0x4f40000 0x0 0x20>; /* DSS_EDP0_INTG_CFG_VP */

- reg-names = "mhdptx", "j721e-intg";

-

- clocks = <&k3_clks 156 19>;

-

- phys = <&torrent_phy_dp>;

- phy-names = "dpphy";

-

- interrupt-parent = <&gic500>;

- interrupts = <GIC_SPI 614 IRQ_TYPE_LEVEL_HIGH>;

-

- power-domains = <&k3_pds 156 TI_SCI_PD_EXCLUSIVE>;

-

- dp0_ports: ports {

- #address-cells = <1>;

- #size-cells = <0>;

- };

- };

-

dphy0: phy@4480000 {

compatible = "ti,j721e-dphy";

reg = <0x0 0x04480000 0x0 0x1000>;