Other Parts Discussed in Thread: TIDA-01568

主题中讨论的其他器件:TIDA-01568

大家好、Sitara 团队

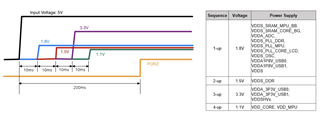

客户希望使用分立式 DCDC/LDO 设计电源轨。

因此他们需要重新检查电源设计。 请查看以下序列和分组域、如果在实际设计中有任何他们需要特别注意的地方、请进行评论。

谢谢。

此致、

插孔

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TIDA-01568

大家好、Sitara 团队

客户希望使用分立式 DCDC/LDO 设计电源轨。

因此他们需要重新检查电源设计。 请查看以下序列和分组域、如果在实际设计中有任何他们需要特别注意的地方、请进行评论。

谢谢。

此致、

插孔

您好、Jack:

感谢您的查询。

时序控制取决于电路板配置。

有关可能的配置、请参阅数据表的以下部分。

6电源和时钟6.1电源6.1.1电源压摆率要求

图6-2. 首选电源时序、双电压 I/O 配置为3.3V

图6-3. 备选电源时序、双电压 I/O 配置为3.3V

图6-4. 电源排序、双电压 I/O 配置为1.8V

图6-5. 禁用内部 RTC LDO 时的电源时序

图6-6. 禁用 RTC 功能时的电源时序

请务必检查以下断电顺序。

6.1.2断电时序

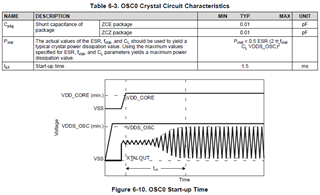

在释放复位之前、请确保时钟稳定。

我们有一个可以参考的 TI 设计。

https://www.ti.com/tool/TIDA-01568

此致、

斯里尼瓦萨

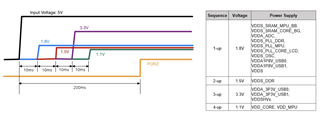

每个电源达到稳定状态的时间如下所示。

- 1.8V 开启时间:100us (LDO)

- 1.5V 开启时间:3.5ms (直流/直流)

- 3.3V 开启时间:200us (LDO)

- 1.1V 导通时间:3.5ms (直流/直流)

问题1: 设计最小时间间隔为3.5ms 是否可以?

问题2. 根据数据表、在施加 VDD_CORE 电压后、时钟信号稳定为1.5ms。

之后可以随时应用 PORZ 信号?

您好、Jack:

感谢您提供宝贵意见。

每个电源达到稳定状态的时间如下所示。

- 1.8V 开启时间:100us (LDO)

- 1.5V 开启时间:3.5ms (直流/直流)

- 3.3V 开启时间:200us (LDO)

- 1.1V 导通时间:3.5ms (直流/直流)

问题1: 设计最小时间间隔为3.5ms 是否可以?

您能否详细说明一下打开时间和时间间隔的含义。

根据数据表,时钟信号在施加 VDD_CORE 电压后稳定为1.5ms。

之后、可以随时应用 PORZ 信号?

这是典型时间、具体取决于 晶体启动+负载电容或所使用的振荡器。

我建议设计 X 2或更多的时钟稳定时间。

此致、

斯里尼瓦萨

您好 Sreenivasa、

感谢您的答复。

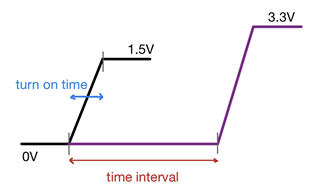

您能否详细说明打开时间和时间间隔的含义。

导通时间指每个电源达到稳定状态所需的时间。

时间间隔是指每个电源的使能信号之间的间隔。

我想知道可以设计的最小时间间隔。

此致、

金敬翰