主题中讨论的其他器件:TDA4VH

尊敬的 TI:

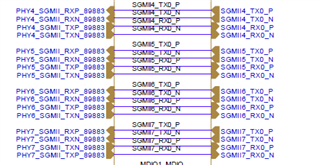

我们的客户板配置端口如下所示:

serdes1->sgmi1/sgmi2/sgmiii3/sgmi4

serdes2->sgmii5/sgmi6/sgmi7/sgmi8

在 DTS 中、服务1和服务2 REFCLK 默认为内部时钟还是外部时钟?

如何设置内部 REFCLK?

请指导我们如何正确配置 SerDes 端口、谢谢

QSGMII 模式:

// SPDX-License-Identifier: GPL-2.0 /** * DT Overlay for CPSW9G in QSGMII mode using J7 Quad Port ETH EXP Add-On Ethernet Card with * J7AHP board. * * Copyright (C) 2022 Texas Instruments Incorporated - https://www.ti.com/ */ #include <dt-bindings/gpio/gpio.h> #include <dt-bindings/mux/ti-serdes.h> #include <dt-bindings/phy/phy-cadence.h> #include <dt-bindings/phy/phy.h> #include <dt-bindings/pinctrl/k3.h> / { aliases { ethernet0 = "/bus@100000/ethernet@c000000/ethernet-ports/port@1"; ethernet1 = "/bus@100000/ethernet@c000000/ethernet-ports/port@2"; ethernet2 = "/bus@100000/ethernet@c000000/ethernet-ports/port@3"; ethernet3 = "/bus@100000/ethernet@c000000/ethernet-ports/port@4"; ethernet4 = "/bus@100000/ethernet@c000000/ethernet-ports/port@5"; ethernet5 = "/bus@100000/ethernet@c000000/ethernet-ports/port@6"; ethernet6 = "/bus@100000/ethernet@c000000/ethernet-ports/port@7"; ethernet7 = "/bus@100000/ethernet@c000000/ethernet-ports/port@8"; }; }; &main_cpsw0 { status = "okay"; pinctrl-names = "default"; pinctrl-0 = <&mdio_pins_default>; }; &main_cpsw0_port1 { status = "okay"; phy-handle = <&cpsw9g_phy0>; phy-mode = "qsgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 1>, <&serdes1_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port2 { status = "okay"; phy-handle = <&cpsw9g_phy1>; phy-mode = "qsgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 2>, <&serdes1_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port3 { status = "okay"; phy-handle = <&cpsw9g_phy2>; phy-mode = "qsgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 3>, <&serdes1_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port4 { status = "okay"; phy-handle = <&cpsw9g_phy3>; phy-mode = "qsgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 4>, <&serdes1_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port5 { status = "okay"; phy-handle = <&cpsw9g_phy4>; phy-mode = "qsgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 5>, <&serdes2_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port6 { status = "okay"; phy-handle = <&cpsw9g_phy5>; phy-mode = "qsgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 6>, <&serdes2_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port7 { status = "okay"; phy-handle = <&cpsw9g_phy6>; phy-mode = "qsgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 7>, <&serdes2_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port8 { status = "okay"; phy-handle = <&cpsw9g_phy7>; phy-mode = "qsgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 8>, <&serdes2_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_mdio { bus_freq = <500000>; //设置500KB #address-cells = <1>; #size-cells = <0>; cpsw9g_phy0: ethernet-phy@0 { reg = <0>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "10000"; }; cpsw9g_phy1: ethernet-phy@1 { reg = <1>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "10000"; }; cpsw9g_phy2: ethernet-phy@2 { reg = <2>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "100"; }; cpsw9g_phy3: ethernet-phy@3 { reg = <3>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "100"; }; cpsw9g_phy4: ethernet-phy@4 { reg = <4>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "100"; }; cpsw9g_phy5: ethernet-phy@5 { reg = <5>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "100"; }; cpsw9g_phy6: ethernet-phy@6 { reg = <6>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "100"; }; cpsw9g_phy7: ethernet-phy@7 { reg = <7>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "100"; }; }; &cpsw9g_virt_mac { status = "disabled"; }; &cpsw9g_virt_maconly { status = "disabled"; }; &main_pmx0 { mdio_pins_default: mdio_pins_default { pinctrl-single,pins = < J784S4_IOPAD(0x05c, PIN_INPUT, 4) /* (AC36) MCASP2_AXR0.MDIO1_MDIO */ J784S4_IOPAD(0x058, PIN_INPUT, 4) /* (AE37) MCASP2_AFSX.MDIO1_MDC */ >; }; }; &main_r5fss0_core0 { firmware-name = "pdk-ipc/ipc_echo_test_mcu2_0_release_strip.xer5f"; }; &serdes_ln_ctrl { idle-states = <J784S4_SERDES0_LANE0_PCIE1_LANE0>, <J784S4_SERDES0_LANE1_PCIE1_LANE1>, <J784S4_SERDES0_LANE2_IP3_UNUSED>, <J784S4_SERDES0_LANE3_USB>, <J784S4_SERDES1_LANE0_QSGMII_LANE3>, <J784S4_SERDES1_LANE1_QSGMII_LANE4>, <J784S4_SERDES1_LANE2_QSGMII_LANE1>, <J784S4_SERDES1_LANE3_QSGMII_LANE2>, <J784S4_SERDES2_LANE0_QSGMII_LANE5>, <J784S4_SERDES2_LANE1_QSGMII_LANE6>, <J784S4_SERDES2_LANE2_QSGMII_LANE7>, <J784S4_SERDES2_LANE3_QSGMII_LANE8>; }; &serdes_wiz2 { status = "okay"; }; &serdes_wiz1 { status = "okay"; }; &serdes2 { status = "okay"; serdes2_qsgmii_link: phy@0 { reg = <0>; cdns,num-lanes = <4>; #phy-cells = <0>; cdns,phy-type = <PHY_TYPE_QSGMII>; resets = <&serdes_wiz2 1>, <&serdes_wiz2 2>, <&serdes_wiz2 3>, <&serdes_wiz2 4>; }; }; &serdes1 { status = "okay"; serdes1_qsgmii_link: phy@0 { reg = <0>; cdns,num-lanes = <4>; #phy-cells = <0>; cdns,phy-type = <PHY_TYPE_QSGMII>; resets = <&serdes_wiz1 1>, <&serdes_wiz1 2>, <&serdes_wiz1 3>, <&serdes_wiz1 4>; }; };

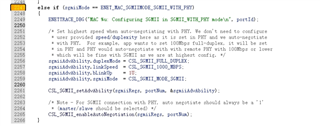

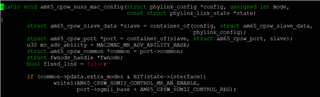

SGMII 模式:

// SPDX-License-Identifier: GPL-2.0 /** * DT Overlay for CPSW9G in QSGMII mode using J7 Quad Port ETH EXP Add-On Ethernet Card with * J7AHP board. * * Copyright (C) 2022 Texas Instruments Incorporated - https://www.ti.com/ */ #include <dt-bindings/gpio/gpio.h> #include <dt-bindings/mux/ti-serdes.h> #include <dt-bindings/phy/phy-cadence.h> #include <dt-bindings/phy/phy.h> #include <dt-bindings/pinctrl/k3.h> / { aliases { ethernet0 = "/bus@100000/ethernet@c000000/ethernet-ports/port@1"; ethernet1 = "/bus@100000/ethernet@c000000/ethernet-ports/port@2"; ethernet2 = "/bus@100000/ethernet@c000000/ethernet-ports/port@3"; ethernet3 = "/bus@100000/ethernet@c000000/ethernet-ports/port@4"; ethernet4 = "/bus@100000/ethernet@c000000/ethernet-ports/port@5"; ethernet5 = "/bus@100000/ethernet@c000000/ethernet-ports/port@6"; ethernet6 = "/bus@100000/ethernet@c000000/ethernet-ports/port@7"; ethernet7 = "/bus@100000/ethernet@c000000/ethernet-ports/port@8"; }; }; &main_cpsw0 { status = "okay"; pinctrl-names = "default"; pinctrl-0 = <&mdio_pins_default>; }; &main_cpsw0_port1 { status = "okay"; phy-handle = <&cpsw9g_phy0>; phy-mode = "sgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 1>, <&serdes1_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port2 { status = "okay"; phy-handle = <&cpsw9g_phy1>; phy-mode = "sgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 2>, <&serdes1_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port3 { status = "okay"; phy-handle = <&cpsw9g_phy2>; phy-mode = "sgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 3>, <&serdes1_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port4 { status = "okay"; phy-handle = <&cpsw9g_phy3>; phy-mode = "sgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 4>, <&serdes1_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port5 { status = "okay"; phy-handle = <&cpsw9g_phy4>; phy-mode = "sgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 5>, <&serdes2_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port6 { status = "okay"; phy-handle = <&cpsw9g_phy5>; phy-mode = "sgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 6>, <&serdes2_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port7 { status = "okay"; phy-handle = <&cpsw9g_phy6>; phy-mode = "sgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 7>, <&serdes2_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_port8 { status = "okay"; phy-handle = <&cpsw9g_phy7>; phy-mode = "sgmii"; mac-address = [00 00 00 00 00 00]; phys = <&phy_gmii_sel_cpsw0 8>, <&serdes2_qsgmii_link>; phy-names = "portmode", "serdes-phy"; }; &main_cpsw0_mdio { bus_freq = <500000>; //设置500KB #address-cells = <1>; #size-cells = <0>; cpsw9g_phy0: ethernet-phy@0 { reg = <0>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "10000"; }; cpsw9g_phy1: ethernet-phy@1 { reg = <1>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "10000"; }; cpsw9g_phy2: ethernet-phy@2 { reg = <2>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "100"; }; cpsw9g_phy3: ethernet-phy@3 { reg = <3>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "100"; }; cpsw9g_phy4: ethernet-phy@4 { reg = <4>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "100"; }; cpsw9g_phy5: ethernet-phy@5 { reg = <5>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "100"; }; cpsw9g_phy6: ethernet-phy@6 { reg = <6>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "100"; }; cpsw9g_phy7: ethernet-phy@7 { reg = <7>; compatible = "ethernet-phy-ieee802.3-c22"; ethphy-mode = "master"; ethphy-speed = "100"; }; }; &cpsw9g_virt_mac { status = "disabled"; }; &cpsw9g_virt_maconly { status = "disabled"; }; &main_pmx0 { mdio_pins_default: mdio_pins_default { pinctrl-single,pins = < J784S4_IOPAD(0x05c, PIN_INPUT, 4) /* (AC36) MCASP2_AXR0.MDIO1_MDIO */ J784S4_IOPAD(0x058, PIN_INPUT, 4) /* (AE37) MCASP2_AFSX.MDIO1_MDC */ >; }; }; &main_r5fss0_core0 { firmware-name = "pdk-ipc/ipc_echo_test_mcu2_0_release_strip.xer5f"; }; &serdes_ln_ctrl { idle-states = <J784S4_SERDES0_LANE0_PCIE1_LANE0>, <J784S4_SERDES0_LANE1_PCIE1_LANE1>, <J784S4_SERDES0_LANE2_IP3_UNUSED>, <J784S4_SERDES0_LANE3_USB>, <J784S4_SERDES1_LANE0_QSGMII_LANE3>, <J784S4_SERDES1_LANE1_QSGMII_LANE4>, <J784S4_SERDES1_LANE2_QSGMII_LANE1>, <J784S4_SERDES1_LANE3_QSGMII_LANE2>, <J784S4_SERDES2_LANE0_QSGMII_LANE5>, <J784S4_SERDES2_LANE1_QSGMII_LANE6>, <J784S4_SERDES2_LANE2_QSGMII_LANE7>, <J784S4_SERDES2_LANE3_QSGMII_LANE8>; }; &serdes_wiz2 { status = "okay"; }; &serdes_wiz1 { status = "okay"; }; &serdes2 { status = "okay"; serdes2_qsgmii_link: phy@0 { reg = <0>; cdns,num-lanes = <4>; #phy-cells = <0>; cdns,phy-type = <PHY_TYPE_SGMII>; resets = <&serdes_wiz2 1>, <&serdes_wiz2 2>, <&serdes_wiz2 3>, <&serdes_wiz2 4>; }; }; &serdes1 { status = "okay"; serdes1_qsgmii_link: phy@0 { reg = <0>; cdns,num-lanes = <4>; #phy-cells = <0>; cdns,phy-type = <PHY_TYPE_SGMII>; resets = <&serdes_wiz1 1>, <&serdes_wiz1 2>, <&serdes_wiz1 3>, <&serdes_wiz1 4>; }; };