您好!

我们有一款带有 AM6442.A PSRAM (MRAM)的定制电路板、通过16位 GPMC 异步非多路复用数据/地址连接。

我根据代码部分基于 AM26xx PSRAM GPMC 示例、部分基于 AM64xx NAND 闪存示例。

很遗憾、当尝试从 PSRAM 中读取时、我收到数据中止错误。 对于我的生命,我不知道这个问题。

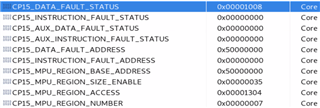

我收到同步外部中止:

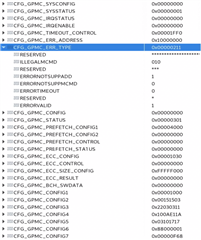

而 GPMC 的 ERRORNOTSUPPADD 错误:

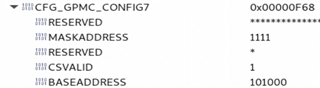

我假设 BASEADDRESS 配置错误、但这是由 GPMC 驱动程序"自动"完成的:

下面是我的代码片段:

/* GPMC attributes */

static GPMC_HwAttrs gGpmcAttrs[CONFIG_GPMC_NUM_INSTANCES] =

{

{

.gpmcBaseAddr = CSL_GPMC0_CFG_BASE,

.dataBaseAddr = CSL_GPMC0_DATA_BASE,

.inputClkFreq = 133333333U,

.intrNum = CSLR_R5FSS0_CORE0_INTR_GPMC0_GPMC_SINTERRUPT_0,

.intrPriority = 4U,

.chipSelBaseAddr = CSL_GPMC0_DATA_BASE,

.chipSelAddrSize = GPMC_CS_MASK_ADDR_SIZE_16MB,

.clkDivider = CSL_GPMC_CONFIG1_GPMCFCLKDIVIDER_DIVBY4,

.waitPinNum = CSL_GPMC_CONFIG1_WAITPINSELECT_W0,

.addrDataMux = CSL_GPMC_CONFIG1_MUXADDDATA_NONMUX,

.timeLatency = CSL_GPMC_CONFIG1_TIMEPARAGRANULARITY_X1,

.waitPinPol = CSL_GPMC_CONFIG_WAIT0PINPOLARITY_W0ACTIVEL,

.timingParams =

{

.csOnTime = GPMC_PSRAM_CS_ON_TIME,

.csRdOffTime = GPMC_PSRAM_CS_RD_OFF_TIME,

.csWrOffTime = GPMC_PSRAM_CS_WR_OFF_TIME,

.advOnTime = GPMC_PSRAM_ADV_ON_TIME,

.advRdOffTime = GPMC_PSRAM_ADV_RD_OFF_TIME,

.advWrOffTime = GPMC_PSRAM_ADV_WR_OFF_TIME,

.advAadMuxOnTime = GPMC_PSRAM_ADV_AADMUX_ON_TIME,

.advAadMuxRdOffTime = GPMC_PSRAM_ADV_AADMUX_RD_OFF_TIME,

.advAadMuxWrOffTime = GPMC_PSRAM_ADV_AADMUX_WR_OFF_TIME,

.weOnTtime = GPMC_PSRAM_WE_ON_TIME,

.weOffTime = GPMC_PSRAM_WE_OFF_TIME,

.oeOnTime = GPMC_PSRAM_OE_ON_TIME,

.oeOffTime = GPMC_PSRAM_OE_OFF_TIME,

.oeAadMuxOnTime = GPMC_PSRAM_OE_AADMUX_ON_TIME,

.oeAadMuxOffTime = GPMC_PSRAM_OE_AADMUX_OFF_TIME,

.pageBurstAccess = GPMC_PSRAM_PAGEBURST_ACCESS_TIME,

.rdAccessTime = GPMC_PSRAM_RD_ACCESS_TIME,

.wrAcessTime = GPMC_PSRAM_WR_ACCESS_TIME,

.rdCycleTime = GPMC_PSRAM_RD_CYCLE_TIME,

.wrCycleTime = GPMC_PSRAM_WR_CYCLE_TIME,

.wrDataOnMuxBusTime = GPMC_PSRAM_ADMUX_DATA_VALID,

.cycle2CycleDelay = GPMC_PSRAM_C2C_DELAY,

.cycleDelaySameChipSel = CSL_GPMC_CONFIG6_CYCLE2CYCLESAMECSEN_NOC2CDELAY,

.cycleDelayDiffChipSel = CSL_GPMC_CONFIG6_CYCLE2CYCLEDIFFCSEN_NOC2CDELAY,

.busTurnAroundTime = GPMC_PSRAM_BRST_TAROUND_TIME,

},

.readType = CSL_GPMC_CONFIG1_READTYPE_RDASYNC,

.csExDelay = CSL_GPMC_CONFIG2_CSEXTRADELAY_NOTDELAYED,

.accessType = CSL_GPMC_CONFIG1_READMULTIPLE_RDSINGLE,

},

};

/* GPMC Driver Parameters */

GPMC_Params gGpmcParams[CONFIG_GPMC_NUM_INSTANCES] =

{

{

.gpmcDmaChIndex = -1,

.devType = CSL_GPMC_CONFIG1_DEVICETYPE_NORLIKE,

.devSize = CSL_GPMC_CONFIG1_DEVICESIZE_SIXTEENBITS,

.chipSel = GPMC_CHIP_SELECT_CS0,

.intrEnable = FALSE,

.dmaEnable = FALSE,

.transferMode = GPMC_TRANSFER_MODE_BLOCKING,

.transferCallBckFunc = NULL,

.memDevice = GPMC_MEM_TYPE_PSRAM,

},

};

int32_t mram_gpmcRead (uint32_t offset, uint8_t *buf, uint32_t len)

{

int32_t status = SystemP_SUCCESS;

uint32_t size = len;

/*if(offset + len > config->attrs->psramSize)

{

status = SystemP_FAILURE;

}*/

uint32_t baseAddress = GPMC_DATA_BASE_ADDRESS;

volatile uint16_t *pSrc = (volatile uint16_t *)(offset+baseAddress);

volatile uint16_t *pDst = (volatile uint16_t *)buf;

uint32_t remain = size & 0x1;

if (remain != 0U)

{

size = size - remain + 2U;

}

while (size != 0U)

{

*pDst = *pSrc;

pSrc++;

pDst++;

size -= 2U;

}

return status;

}

我非常感谢您的支持。

您好

斯特凡