您好!

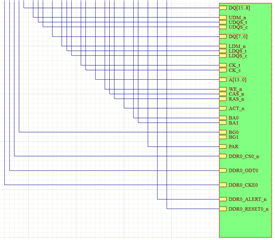

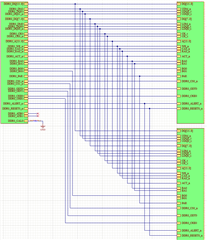

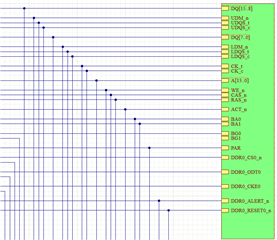

参考《AM620x DDR 设计指南》 https://www.ti.com/lit/an/sprad06/sprad06.pdf 、我看到了这个屏幕截图、其中显示了与微处理器的16位 DDR 连接。 其中、 DDR0_BG1、DDR0_CS1、DDR0_ODT1和 DDR0_CKE1引脚未连接。

TI 是否明白为何上述未连接线路上不能连接第二个 DDR 接口? 显示的所有其他信号线都将在两个器件之间共享。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

参考《AM620x DDR 设计指南》 https://www.ti.com/lit/an/sprad06/sprad06.pdf 、我看到了这个屏幕截图、其中显示了与微处理器的16位 DDR 连接。 其中、 DDR0_BG1、DDR0_CS1、DDR0_ODT1和 DDR0_CKE1引脚未连接。

TI 是否明白为何上述未连接线路上不能连接第二个 DDR 接口? 显示的所有其他信号线都将在两个器件之间共享。

您好、James:

我忘记了提及、我尝试连接的第二个 DDR 接口也是 x16、而不是两个 x8。 这就是我构想信号连接的方法。

这是我最初感到困惑的原因,也是我来到论坛讨论的原因。

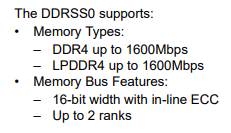

技术参考手册的第9.1节说明 DDRSS 最多可以支持2个等级。

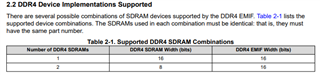

这似乎与表2-1相矛盾。 《DDR 电路板设计和布局指南》中支持的 DDR4 SDRAM 组合、表示只能有一个 x16 SDRAM。 但是、我认为这是指单列的可能组合、而不是可支持的器件总数。

那么、是否只支持一个 x16 DDR 器件、或者是否可以如上所示连接两个 x16器件?

谢谢!

如果您看不到信号名称、此处将显示放大的屏幕截图。

左上角-

右上角-

右下角-