主题中讨论的其他器件:TDA4VH

您好、TI 专家!

客户正在处理 TDA4VH SDK9.0客户板 ,引导模式为 SPL 。

它们具有 使用 SD 卡启动时没有问题 那样。

最近、由于他们的项目即将实现大规模生产、他们需要 更改以使用 eMMC 引导 ,并且发现了以下问题。

首先、他们使用的是 西部数码(自有 SanDisk 公司) SDINBDG4-16G-XI1 ,相应的数据表如下所示。

e2e.ti.com/.../SDINBDG4_2D00_Industrial.pdf

问题是、它需要一个 eMMC 引导失败的可能性很大 ,只有一个 使 eMMC 能够成功启动 。 (室温下)

当 eMMC 引导失败时、它将具有 以下3个不同的错误日志 。

错误日志1:

错误日志2:

错误日志3:

如果 eMMC 成功引导,它将具有以下成功引导日志(HS400):

我们已完成硬件和软件调试测试、我已在下面进行了总结、请查看结果、谢谢!

测试1

我们已尝试将下面的 regmap_RED_POLL_TIMEOUT 参数从20增加到2000、结果表明 eMMC 引导成功的可能性提高了一点、但仍然有机会发生上述引导失败。

测试2

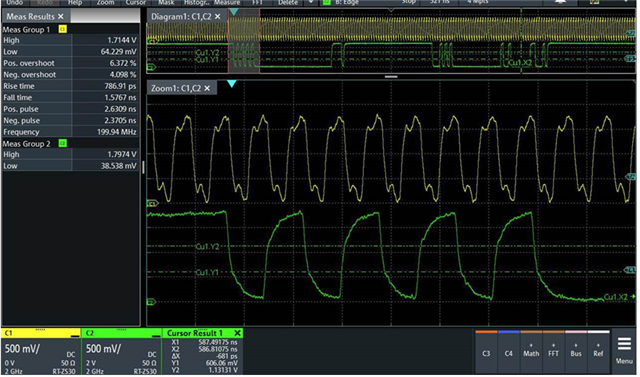

我们已经检查了 时钟和 D0以及 DS 的波形、其 在下面看起来很正常。

测试3

我们已测试了 eMMC 延迟、 下面的测试数据看起来是正常的。

测试4

我们已在高速模式(50MHz)下进行了测试、根据 JESD84-B51标准的要求、CMD 信号的保持时间似乎不够。 此外、在高速模式下、只有在 eMMC 引导成功时才能捕获波形、并且只能在内核引导阶段捕获波形。 请查看以下内容。

从上面的测试数据中可以看到、输入 CMD 保持时间为1.706ns。

但是、根据下面显示的标准的要求、保持时间的最小值应为3ns。

该结果是否与我们的 eMMC 启动问题有关?

我们怀疑这意味着时间差是不够的,但我们不是很确定。

测试5

根据测试4结果、我们已尝试以下实验。 在下面的 MMC0_CMD 行(图片显示了默认的硬件原理图、没有任何更改)中、我们已尝试将 R3808从0Ω 更改为10Ω,、并并联添加了一个非常小的电容器 C4918 (4.7pF)。

结果表明、在更改硬件后、我们每次都可以在 HS400模式下成功引导 eMMC。

但是、以下原因导致我们无法采用该解决方案来解决此问题。

我们已在如下所示的默认硬件设置中仔细检查了时钟和 CMD 的时间系列、 它实际上已经满足 eMMC 标准中的总线时序

进行上述硬件更改后、时钟和 CMD 的时间系列不如以前那样好、如下所示。

我们可以看到、尽管我们可以通过此方法成功引导 eMMC、但波形变得很差(不像预期的方波)。

另外、我们已经在添加电阻器和电容器后检查了 CMD 保持时间、可以看到保持时间更接近所需的最低要求3ns (从1.7ns 更改为2.0ns)。 如果添加了更大的电容、则保持时间将达到标准要求3ns、但增加的电容越大 、波形越差、它完全不像方波、因此我们无法采用该解决方案。

对于我们的设计、另一个重要信息是、我们有两代电路板。 在第一代中、PCB 布线长度为 1770密耳 。 在第二代器件中、PCB 布线长度优化为 1370mil 。 对于相同的软件设置、它可以在第一代电路板上以 HS400模式成功引导 eMMC、但对于第二代电路板、会出现上述问题。 我们已测试 TDA4VH EVM 的 PCB 布线长度 2000密耳 。 我们能否怀疑默认 EVM 设计的时序裕度不够充分、因此如果我们优化 PCB 布线长度、可能会有这个问题?

我们可能需要根据我们的实验结果获得一些建议,谢谢!

我们还发现、一些类似的帖子最近具有如下所示的相同错误日志。

我们希望获得基于这些信息的进一步调试建议、感谢您的帮助!

此致、

凯文