您好

您能否提供 EDMA 在乒乓模式和 McBSP 中断模式下的使用示例

您之前提供的示例没有 McBSP 中断。

需要注意的是、McBSP 中断事件位于表6-27 CIC0事件表中。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

您能否提供 EDMA 在乒乓模式和 McBSP 中断模式下的使用示例

您之前提供的示例没有 McBSP 中断。

需要注意的是、McBSP 中断事件位于表6-27 CIC0事件表中。

Doron、

为了确保 McBSP 外设正常工作、TI 只能提供环回示例。

使用 McBSP 外设以及音频 ADC/DAC 或 AIC 的客户可以使用实际中断进行测试、例如:

/*寄存器 McBSP 中断*/

//McbspRcvInterrupt_init (hMcbspRxChan);

//McbspXmtInterrupt_init (hMcbspTxChan);

客户必须根据为 McBSP 选择的接口器件自行调整。

此致

尚卡里

//***************************************************************************

// Function: SerialPortSWI

// Type: Void

//

// Purpose: This function is a software interrupt service routine

// This function called by hardware interrupt service routine.

// Optimized by Gilad Z.

//

// Inputs: NONE

// Outputs: NONE

//

//***************************************************************************

#pragma CODE_SECTION(SerialPortSWI, "SerialPortSWI_Sect");

Void SerialPortSWI(Void)

{

S16 i,k;

S16 NumOfEntries;

*(U32*)0x01848214 = 0;

*(U32*)0x01848214 = 1;

}

//***************************************************************************

// Function: SerialPortHWI

// Type: Void

//

// Purpose: This function is a hardware interrupt service routine.

// It posts the software interrupt.

//

//

// Inputs: NONE

// Outputs: NONE

//

//***************************************************************************

//#pragma CODE_SECTION(SerialPortHWI, "IRAM");

void SerialPortHWI(void)

{

System_printf ("Debug(Core %d): SerialPortHWI serviced\n", coreNum);

Swi_post(SWI_SerialPort_Rx);

}

//#endif

void Mcbsp_interrupt_init(void)

{

Hwi_Params hwi_params;

static Bool port0Init = FALSE;

Bool error_flag;

if (!port0Init)

{

error_flag = FALSE;

Hwi_Params_init (&hwi_params);

/*

* Setup TX Int using BIOS6 Hwi module

*/

hwi_params.arg = (UArg) 0;

hwi_params.enableInt = 1;

hwi_params.eventId = CIC0_OUT; //EDMA3_CC_INT1; //APP_EMAC0_TX_INT_EV;

hwi_params.maskSetting = ti_sysbios_hal_Hwi_MaskingOption_SELF;

if (Hwi_create (APP_MCBSP0_TXINT_ID, (ti_sysbios_hal_Hwi_FuncPtr) &SerialPortHWI, &hwi_params, NULL) == NULL)

{

error_flag = TRUE;

}

if(!error_flag)

{

port0Init = TRUE;

edmaEnterSingleCoreCriticalSection(0);

}

}

}

/**

* @b Description

* @n

* The function is used to provide critical section to prevent access of shared

* resources from single core and multiple threads.

*

* @param[in] port_num

* EMAC port number which needs critical section to protect its resources.

*

* @retval

* None

*/

void

edmaEnterSingleCoreCriticalSection

(

Uint32 port_num

)

{

IER &= ~APP_MCBSP0_INT_FLAG;

}

void EnableMCBSPInterrupts(void)

{

unsigned int intState;

/* Disabling the global interrupts */

intState = Hwi_disable();

/* route Ecc error event 110 (system event) at CIC0/1 to event (CIC0_OUT0 Or CIC1_OUT0) at cic0/1_out (host event)*/

/* those CIC0/1_out are maped to event 102 at CorePac (broadcast event) [figure 7-32 at tms320c6678]*/

//CpIntc_mapSysIntToHostInt(0, MCBSP_RXV_EVENT_ID, 0 /*CICO/1_OUT0*/);

CpIntc_mapSysIntToHostInt(0, 32, 0 /*CICO/1_OUT0*/);

//CpIntc_enableSysInt(0, MCBSP_RXV_EVENT_ID);

CpIntc_enableSysInt(0, 32);

CpIntc_enableHostInt(0, 0 /*CICO/1_OUT0*/);

/* event 102 at CorePac is routed, and configured through the events combiner (Shannon.cfg)*/

/* Restore interrupts */

Hwi_restore(intState);

}Doron、

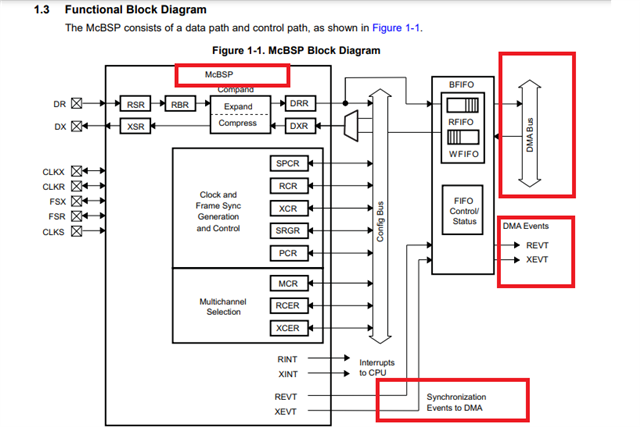

根据 C6657的 McBSP 功能方框图、数据传输通过 EDMA 传输控制器进行。

EDMA 会提供示例代码。

"在 C665x 器件上有一个 EDMA 通道控制器:EDMA3_CC。 它有四个传输控制器:TC0、TC1、TC2和 TC3。 在本文档中、与 CC 关联的 tcx 被称为 EDMA3_CC_tcx。 每个传输控制器都直接连接到交换机结构。 第9.2节列出了传输控制器能够访问的外设。"

外设列表中的一个是 McBSP。

如需更多信息、请参阅

https://www.ti.com/lit/ds/symlink/tms320c6657.pdf 第9.1节

https://www.ti.com/lit/ug/spruhh0/spruhh0.pdf 第1.3节

此致

尚卡里