主题中讨论的其他器件:TDA4VH

是否可以在 R5F 内部高速缓存存储器上进行 ECC (SEC/DED)测试? 如果是、请提供相关步骤。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

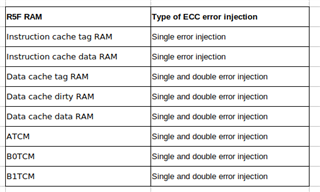

根据设计团队的输入、下表列出了 R5F 缓存的类型和支持的错误注入类型:

因此、I Cache 上不支持 DED。 注意:ECC 聚合器支持注入、但不支持检查和报告。 这是 ARM IP 限制、因为无法从 I Cache 中的 DED 错误中恢复。

以下是在 TDA4VH 的 R5F 缓存上测试 SEC/DED 的步骤:

1.在初始化高速缓存存储器之前、通过将位于 sdl/test/r5f_startup 的 void __mpu_init (void)文件中的 startup.c 中的 ACTLR 寄存器设置为0xE000028、为高速缓存配置 ECC。

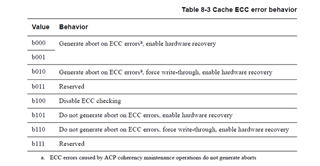

分配给此寄存器的值完全取决于您的特定用例。 我们不建议为该寄存器使用任何刚性值。 但是、 考虑到 single-bit 错误会自动纠正、因此避免因可纠正的错误而中止是合乎逻辑的。 因此、您可以考虑将 ACTLR 寄存器设置为101、这将导致仅针对不可纠正的错误的中止。

asm("MRC p15, 0, r0, c1, c0, 0"); // Read System Control Register

asm("BIC r0, r0, #0x1 << 2"); // Disable data cache bit

asm("BIC r0, r0, #0x1 << 12"); // Disable instruction cache bit

asm("DSB");

asm("MCR p15, 0, r0, c1, c0, 0"); // Write System Control Register

asm("ISB"); // Ensures following instructions are not executed from cache

asm("MRC p15, 0, r1, c1, c0, 1"); // Read Auxiliary Control Register

asm("ORR r1, r1, #(0x5 << 3)"); //Enable ECC for Cache

asm("MCR p15, 0, r1, c1, c0, 1"); // Write Auxiliary Control Register

asm("MCR p15, 0, r0, c15, c5, 0"); // Invalidate entire data cache

asm("MCR p15, 0, r0, c7, c5, 0"); // Invalidate entire instruction cache

asm("MRC p15, 0, r0, c1, c0, 0"); // Read System Control Register

asm("ORR r0, r0, #0x1 << 2"); // Enable data cache bit

asm("ORR r0, r0, #0x1 << 12"); // Enable instruction cache bit

asm("DSB");

asm("MCR p15, 0, r0, c1, c0, 0"); // Write System Control Register

asm("ISB"); 2.启用 R5F PMCR 寄存器的导出功能,将缓存事件路由到 ESM/ Pulsar 寄存器。

asm("MOV R5, #0x0");

asm("MRC P15,#0, R5, C9, C12,#0");

asm("ORR R5, R5, #0x2"); // Reset event counter

asm("MCR P15,#0, R5, C9, C12,#0");

asm("MRC P15,#0, R5, C9, C12,#0");

asm("ORR R5, R5, #0x11");

asm("MCR P15,#0, R5, C9, C12,#0");

asm("MOV r4, #0x60");

asm("MCR p15,#0,r4,c9,c13,#1"); 3. 使用 SDL_ESM_init () API 初始化 ESM 模块。

4.通过将32KB 的数据从 DDR 复制到随机阵列来填充高速缓存。

#define ARRAY_SIZE 32*1024 // Size of the array in bytes (32KB)

uint8_t a[ARRAY_SIZE];

uint8_t b[ARRAY_SIZE];

for(uint32_t iii=0;iii<ARRAY_SIZE;iii++)

{

a[iii]=(iii%256)+1;

} 5.在 R5F 内核中执行错误注入。

a.对于 single-bit 错误注入:

uint32_t *ptr2=(uint32_t *)0x40080008; //Set RAM ID *ptr2=0x8; uint32_t *ptr3=(uint32_t *)0x40080014; // ECC Ctrl Reg *ptr3=0x28;// 0x28 for Data RAM IDs, 0x68 for Tag RAM IDs asm("NOP"); //Enable ECC for Cache memories, Inject error into RAM ID 8

b.对于双位错误注入:

uint32_t *ptr2=(uint32_t *)0x40080008; //Set RAM ID *ptr2=0x8; uint32_t *ptr4=(uint32_t *)0x4008001C; //ECC Error Control2 reg *ptr4=0x30002; uint32_t *ptr3=(uint32_t *)0x40080014; // ECC Ctrl Reg *ptr3=0x70;// 0x30 for Data RAM IDs, 0x70 for Tag RAM IDs asm("NOP"); //Enable ECC for Cache memories, Inject error into RAM ID 8

6.访问高速缓存区域以触发错误

for(uint32_t i=0;i<ARRAY_SIZE;i++) { b[i]=a[i]; }

对于任何具有仅注入端点(如 TCM 和高速缓存存储器)的 IP/模块(如 R5F)、错误报告不是通过 ECC 聚合器而是通过 IP/模块本身进行的。 在这种情况下、通过来自 R5F 本身的错误通知来触发它自己的 ESM 事件。

为了验证错误注入、可在 ESM_STS_j 寄存器中监控以下 ESM 事件(偏移= 420h +公式、(基址0x40800400):

#define SDLR_MCU_ESM0_ESM_LVL_EVENT_MCU_R5FSS0_COMMON0_ECC_SE_TO_ESM_0_0 (50U)

#define SDLR_MCU_ESM0_ESM_LVL_EVENT_MCU_R5FSS0_COMMON0_ECC_DE_TO_ESM_0_0 (51u)

可以在 ESM_init 中启用上述 ESM 错误事件以在检测到错误时接收回调。

此致、

约西塔