您想要实现的功能:

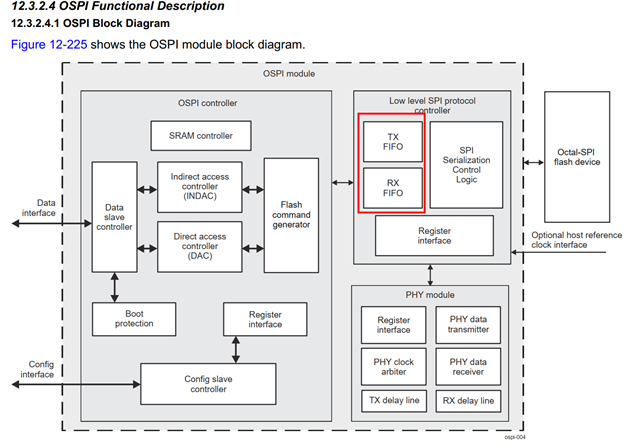

1.通过访问 OSPI 的 TX-FIFO 和 RX-FIFO 来发送和接收数据

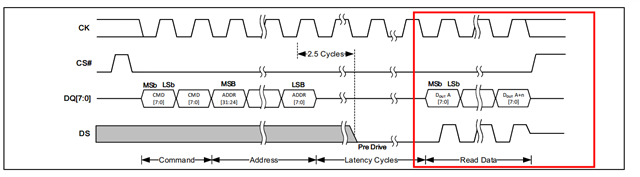

2.通过8条线路接收或发送数据

当前配置为使用传统模式、8位地址、数据和命令模式。 发送时可测量 CLK 和 DQ[0-8]。 接收时没有 CLK 信号、无法读取该值。 具体的配置寄存器值如下所示。 请见下方。 什么原因?

CONFIG_REG = 80783981 DEV_INSTR_RD_CONFIG_REG = 133300 DEV_INSTR_WR_CONFIG_REG = 1f033002 DEV_DELAY_REG = a0a0a0a RD_DATA_CAPTURE_REG = 0 DEV_SIZE_CONFIG_REG = 81002 SRAM_PARTITION_CFG_REG = 3f IND_AHB_ADDR_TRIGGER_REG = 4000000 DMA_PERIPH_CONFIG_REG = 0 REMAP_ADDR_REG = 0 MODE_BIT_CONFIG_REG = 200 SRAM_FILL_REG = 0 TX_THRESH_REG = 1 RX_THRESH_REG = 1 WRITE_COMPLETION_CTRL_REG = 10005 NO_OF_POLLS_BEF_EXP_REG = ffffffff IRQ_STATUS_REG = 0 IRQ_MASK_REG = f7fff LOWER_WR_PROT_REG = 0 UPPER_WR_PROT_REG = 0 WR_PROT_CTRL_REG = 0 INDIRECT_READ_XFER_CTRL_REG = 0 INDIRECT_READ_XFER_WATERMARK_REG = ffffffff INDIRECT_READ_XFER_START_REG = 0 INDIRECT_READ_XFER_NUM_BYTES_REG = 0 INDIRECT_WRITE_XFER_CTRL_REG = 0 INDIRECT_WRITE_XFER_WATERMARK_REG = ffffffff INDIRECT_WRITE_XFER_START_REG = 0 INDIRECT_WRITE_XFER_NUM_BYTES_REG = 0 INDIRECT_TRIGGER_ADDR_RANGE_REG = 4 FLASH_COMMAND_CTRL_MEM_REG = 0 FLASH_CMD_CTRL_REG = 0 FLASH_CMD_ADDR_REG = 0 FLASH_RD_DATA_LOWER_REG = 0 FLASH_RD_DATA_UPPER_REG = 0 FLASH_WR_DATA_LOWER_REG = 0 FLASH_WR_DATA_UPPER_REG = 0 POLLING_FLASH_STATUS_REG = 0 PHY_CONFIGURATION_REG = 0 PHY_MASTER_CONTROL_REG = 800000 DLL_OBSERVABLE_LOWER_REG = ff81f9 DLL_OBSERVABLE_UPPER_REG = 0 OPCODE_EXT_LOWER_REG = 13edfa00 OPCODE_EXT_UPPER_REG = 6f90000 MODULE_ID_REG = 3000300

static int32_t xg_ospi_reg_read(OSPI_Handle handle)

{

OSPI_v0_HwAttrs const *hwAttrs = NULL;

int32_t regVal = 0;

CSL_ospi_flash_cfgRegs *pRegs;

int32_t val;

hwAttrs = (OSPI_v0_HwAttrs const *)handle->hwAttrs;

pRegs = (CSL_ospi_flash_cfgRegs *)(hwAttrs->baseAddr);

CSL_REG32_WR(hwAttrs->dataAddr, 0x555aa5aa);

wait_idle(handle);

//val = CSL_REG32_RD(&pRegs->CONFIG_REG);

//UART_printf("----------xiongg %s %d: config reg = %x\n",__FUNCTION__,__LINE__, val);

val = CSL_REG32_RD((char *)hwAttrs->dataAddr);

UART_printf("----------xiongg %s %d: val = %x\n",__FUNCTION__,__LINE__, val);

return 0;

}

只有4个脉冲才能写入4个字节的数据

读取数据为0