主题中讨论的其他器件:CDCE62005、 CDCE6214、 CDCE62002、 LMK03318、LMK04208

您好!

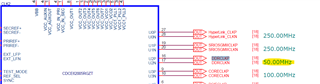

正如我在 EVB 原理图中看到的、有两个 DDRCLK、这似乎不合逻辑、

您能告诉我、哪个 DDRCLK 是正确的吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Daniel / kcastille、

为 CDCE62005 时钟发生器相当耗电、并且容易出现高温-在实际系统中、推荐使用 CDCE6214。

在这种情况下、建议使用散热器或风扇来降低器件温度。

之前、该器件在评估模块上的热性能会令人难以置信: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/336757/cdce62005-clock-ic-getting-heated-up-in-tms320c6670-evaluation-board?tisearch=e2e-sitesearch&keymatch=cdce62005%25252520heat#

谢谢。

卡德姆

Daniel:

如果输入时钟为50 MHz、

DDR OutFreqMhz = 2 x inFreq x mult / postdiv = 2 x 50 x 20 / 2 = 1000 MHz

----------------

如果输入时钟为66.667 MHz、

DDR OutFreqMhz = 2 x inFreq x mult / postdiv = 2 x 66.667 x 2 x 20 / 2 = 1333.3 MHz

DDR 时钟可根据需要改变。

有关时钟乘法器和除法器的更多详细信息、请参阅 C6657的 GEL 文件

---

在 EVM 页面中、他们应该一直维护所有页面中的50 MHz 或66.667 MHz。

由于 DDR3内存的标准速度均为1333 MT/s、因此我建议您考虑输入时钟为66.667。

此致

尚卡里

Daniel:

在前面的多个线程中、由于 CDCE62005的过热问题、我们建议使用 CDCE62002来代替 CDCE62005。

如果需要三个输出、则可能需要一个 LMK 器件、例如 LMK03318、其性能优于 CDC 器件:

LMK03318的典型 LVDS 上升/下降时间符合前面指定的标准:

或者、为了尽可能降低功耗、LMK04208可用作时钟发生器(以更大范围为代价):

随附了一份完整的器件报告、这些器件能够以 LVDS 输出格式生成这三种输出频率-请注意、并非所有器件都满足压摆率要求:

e2e.ti.com/.../cta_2D00_export_5F00_2023_2D00_9_2D00_13_5F00_11_3B00_55_3B00_23.pdf

谢谢。

卡德姆