主题中讨论的其他器件: SysConfig

SDK 中的 GPIO_LED_BLINK 示例适用于 LP-AM263上的红色 LED。

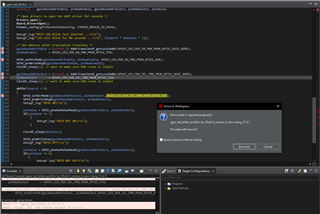

为了测试 GPIO 分配、我修改了该基本示例。

我将外部 LED 连接到 Booster Pack 接头 J4上的引脚33 、

使用 SysConfig 将 PRO_PRU0_GPIO0分配给它、

GPIO93设置为标准 多路复用 模式7.

此修改后的闪烁程序 在处理器内存中似乎可以正常工作、但外部 LED 不闪烁。

当外部 LED 由另外3.3V 电源供电时工作正常。

但这里不是 Booster Pack 接头 J4上的引脚33上具有该程序。

SysConfig 在 ti_pinmux_config.c 中进行的多路复用配置为:

静态 Pinmux_Per Ccfg_t gPinMuxMainDomainCfg[]={

/* GPIO0引脚配置*/

/* GPIO26 -> UART0_CTSN (B7)*/

{

PIN_UART0_CTSN、

( PIN_MODE(7)| PIN_pull_disable | PIN_SLEW_RATE_HIGH | PIN_QUAL_SYNC | PIN_GPIO_R5SS0_0 )

}、

/* GPIO0引脚配置*/

/* GPIO93 -> PR0_PRU0_GPIO0 (K17)*/

{

PIN_PR0_PRU0_GPIO0、

( PIN_MODE(7)| PIN_pull_disable | PIN_SLEW_RATE_HIGH | PIN_QUAL_SYNC | PIN_GPIO_R5SS0_0 )

}、

/* GPIO0引脚配置*/

/* GPIO94 -> PR0_PRU0_GPIO1 (K18)*/

{

PIN_PR0_PRU0_GPIO1、

( PIN_MODE(7)| PIN_pull_disable | PIN_SLEW_RATE_HIGH | PIN_QUAL_SYNC | PIN_GPIO_R5SS0_0 )

}、

/* GPIO0引脚配置*/

/* GPIO96 -> PR0_PRU0_GPIO3 (J17)*/

{

PIN_PR0_PRU0_GPIO3、

( PIN_MODE(7)| PIN_pull_disable | PIN_SLEW_RATE_HIGH | PIN_QUAL_SYNC | PIN_GPIO_R5SS0_0 )

}、

/* UART0引脚配置*/

/* UART0_RXD -> UART0_RXD (A7)*/

{

PIN_UART0_RXD、

( PIN_MODE(0)| PIN_PULL_DISABLE | PIN_SLEW_RATE_LOW )

}、

/* UART0_TXD -> UART0_TXD (A6)*/

{

PIN_UART0_TXD、

( PIN_MODE(0)| PIN_PULL_DISABLE | PIN_SLEW_RATE_LOW )

}、

{PINMUX_END、PINMUX_END}

};

如果处理器焊盘 K17连接到 Booster Pack 接头 J4的引脚33、则这应该起作用。

为什么这不起作用?

非常感谢您的帮助。

此致

罗伯特