工具与软件:

Im 使用 uPP 协议在 FPGA 和 C6655之间进行通信。 但我在 ypisr 寄存器中指出一个 erri 错误。 即内部总线错误。 我认为这是 PLL 配置错误造成的。 您能否提供一些有关如何为 uPP 模块时钟执行此操作的见解。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

Im 使用 uPP 协议在 FPGA 和 C6655之间进行通信。 但我在 ypisr 寄存器中指出一个 erri 错误。 即内部总线错误。 我认为这是 PLL 配置错误造成的。 您能否提供一些有关如何为 uPP 模块时钟执行此操作的见解。

Mounika,

我们可以在这里找到 uPP 用户指南:- https://www.ti.com/lit/ug/spruhg9/spruhg9.pdf

在 MCSDK -多核软件开发套件- TI 提供的软件包中、可能有一些 uPP 的示例代码。

请看一下示例代码中使用的配置。

https://www.ti.com/tool/BIOSLINUXMCSDK

此致

Shankari G.

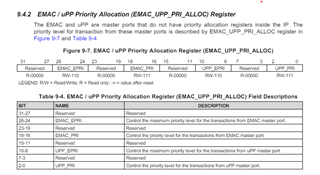

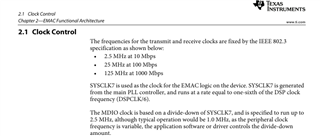

我们面临的问题是 upp 的 upisr 寄存器中存在 erri 错误、 我之前已经提到过、这是由模块时钟产生的 、uPP 是错误的。 我们得到的频率是 166 MHz (sysclok 1000MHz EMAC/6)= 166 MHz、它是 EMAC 的频率 (dspclock /6)。

由于默认情况下 upp 和 EMAC 具有相同的低优先级、我认为这种情况是这样发生的、通过将 upp 优先级更改为"urgent"、这个问题将得到解决、或者您有任何其他的建议或任何其他的配置、以便解决 erri 总线错误问题。

谢谢

Mounika,

路径上的"Low Level register configuration"(低级寄存器配置)--

TI/CSL/CSL/V3/UPP/V0/cslr_upp.h src 在封装中、

PROCESSOR-SDK-RTOS - C665x 06_03_00_106 - http://software-dl.ti.com/processor-sdk-rtos/esd/C665x/latest/index_FDS.html

——

此处的示例代码:-

e2e.ti.com/.../0654.upp_5F00_dlb_5F00_test.zip

更多有关在 CCS 中构建该项目的信息、请参阅此 E2E:-

然后向下滚动一位

此致

Shankari G.