主题中讨论的其他器件:SysConfig、

工具与软件:

尊敬的专家:

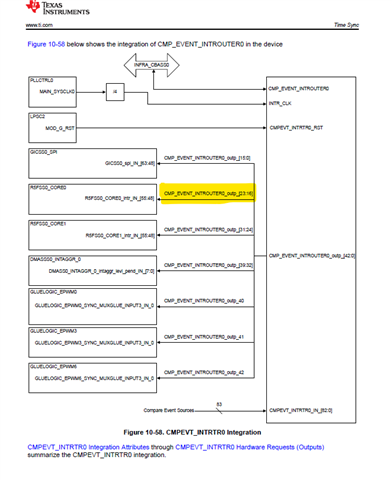

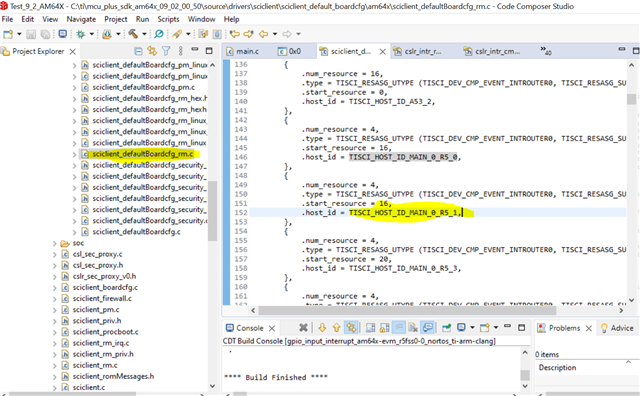

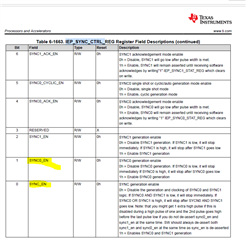

我对主域内核(A53和 R5)之间的内核间时间同步路由有疑问。

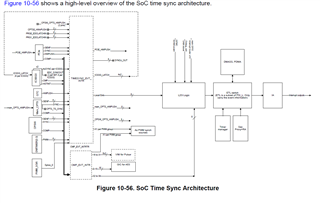

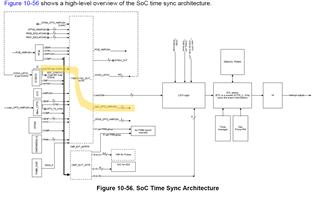

我的目标是将我在 Linux 中通过在 A53内核中运行的 ICSSG0接收到的时间信号路由到在 R5内核中运行且具有时间同步路由器机制的 MCU 应用、从而提供内核间时钟同步。

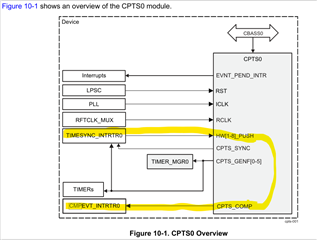

我是否可以在不使用 CPTS 的情况下在 Linux 器件树中执行此操作?

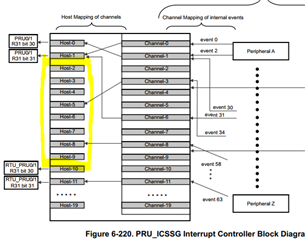

我的意思是、我能否将 AM64X_DEV_PRU_ICSSG0的输出直接路由到 TSR 模块本身、并在 MCU 应用中将 TSR 的输出作为中断接收?

当我检查 TSR 输出源时、我无法看到为 TSR 本身保留的输出信号或中断。

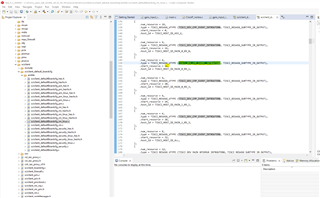

如果可能、请为设备树共享一个示例 timsesync_router 节点。

路由映射 可能与此类似:PRU-ICSSG0 -> A53 -> TSR -> R5

ı 的另一个问题是、这样是否不可能使用 CPT 路由时间信号?

其他的路由映射可能 与此类似:PRU-ICSSG0 -> A53 -> TSR -> CPTS -> R5

我的最后一个问题是、我不熟悉 R5内核中 MCU 实现中的中断处理机制。

您能不能提供一些有关 TSR 中断处理的信息?

如何使用 TSR 输出来更新 R5的系统时钟?

CCS:12.5.00007

MCU+ SDK:v09.01.00.41

SysConfig:1.18.0

SoC:AM6442

此致、金枪鱼 Girişken