This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的专家:

我对主域内核(A53和 R5)之间的内核间时间同步路由有疑问。

我的目标是将我在 Linux 中通过在 A53内核中运行的 ICSSG0接收到的时间信号路由到在 R5内核中运行且具有时间同步路由器机制的 MCU 应用、从而提供内核间时钟同步。

我是否可以在不使用 CPTS 的情况下在 Linux 器件树中执行此操作?

我的意思是、我能否将 AM64X_DEV_PRU_ICSSG0的输出直接路由到 TSR 模块本身、并在 MCU 应用中将 TSR 的输出作为中断接收?

当我检查 TSR 输出源时、我无法看到为 TSR 本身保留的输出信号或中断。

如果可能、请为设备树共享一个示例 timsesync_router 节点。

路由映射 可能与此类似:PRU-ICSSG0 -> A53 -> TSR -> R5

ı 的另一个问题是、这样是否不可能使用 CPT 路由时间信号?

其他的路由映射可能 与此类似:PRU-ICSSG0 -> A53 -> TSR -> CPTS -> R5

我的最后一个问题是、我不熟悉 R5内核中 MCU 实现中的中断处理机制。

您能不能提供一些有关 TSR 中断处理的信息?

如何使用 TSR 输出来更新 R5的系统时钟?

CCS:12.5.00007

MCU+ SDK:v09.01.00.41

SysConfig:1.18.0

SoC:AM6442

此致、金枪鱼 Girişken

您好、Tuna、

我今天没有电力或互联网、电力可能会耗尽几天(我必须开车到另一个城市才能键入此回复)。 因此我的回答可能会延迟-如果您下周还在等待我的回复、可以随意地通过 ping 通该主题。

同时、我将向您的另一个团队成员分配您的线程、以评论您关于 MCU+ SDK R5F 内核内的中断处理的问题。

此致、

Nick

您好、Nick。

感谢 您的关注。 我希望你能在本周尽早作出回应。 如果您的团队成员熟悉时间同步或处理时间同步中断、能够为我提供帮助、我也将不胜感激。

此致、金枪鱼 Girişken

您好、Tuna、

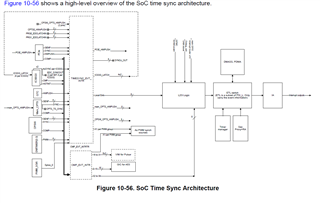

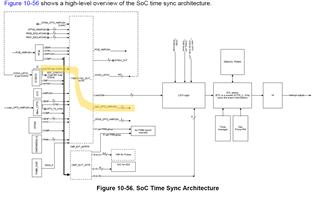

请查看以下章节、并查看您的应用应该需要哪条路径。

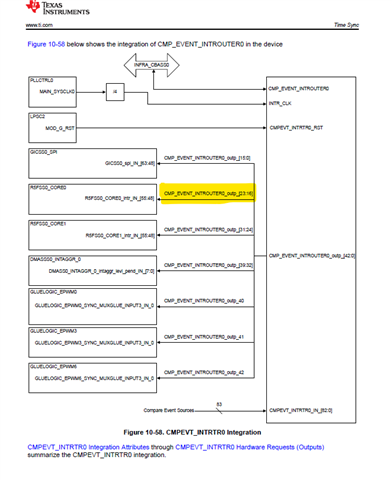

从 ICSSG、一些比较和 HSINT 事件会路由到从 CMP 事件 INTR 到 A53内核和 R5F 内核的路径。

另外、4个 SYNC 信号连接到时间同步路由器来提供不同的输出。

此致、

Anil。

感谢您的回复、

如果我在 TIMESYNC_ROUTER 节点下的 Linux 设备树中进行如下更改、是否会自动生成中断?

&TIMESYNC_ROUTER{ pinctrl-names ="默认值";pinctrl-0 =<&icssg_cpts_pps>; /*时间同步路由示例*/ icssg_cpts_pps:icssg_cpts_pps{ PINCTL-SINGLE、PINS =< /* pps [pr1_edc0_sync0_out] in29 -> out16 [CPTS_HW1_PUSH]*/ TS_OFFSET (16、29) >; }; };

同时、我需要在下面执行的中断吗?

R5FSS0_CORRE0_INTR_IN_129129 CPTS0_EVNT_pend_0

此致、金枪鱼 Girişken。

您好、Tuna、

在 RTOS 端、通常这些路由器应通过 SCI 客户端进行配置、我假设 Linux 端也应如此。

对于 Linux、我们将得到 Linux 团队的帮助。

此致、

Anil。

您好、Tuna、

请告诉我们更多有关您用例的信息。

时间主控器:

您使用的是通用 PRU 应用还是 PRU 以太网?

您是否正在将时间从 PRU 以太网的外部时间主控获得?

如果您使用 PRU 以太网、PRU 子系统是由 Linux 控制还是由 R5F 内核控制?

此致、

Nick

您好、Nick。

我直接 在 Linux 端使用 PRU IEP 作为主时钟、并可以将 Linux 的系统时钟与 phy2sys 程序同步。

但同时、我在 R5内核上有一个 MCU 应用程序。

此应用通过我在 SysConfig 中设置的计时器有自己的系统时钟计数器、此计数器每毫秒线性增加一次。

我的目标是在我在 Linux 中通过 PRU IEP 生成的 pps 信号的每个上升沿上生成从 A53内核到 R5内核的中断。

我计划将两个内核的时钟与每秒出现的中断进行同步。

我设法生成了文档( software-dl.ti.com/.../PRU_ICSSG_Ethernet.html )中所述的 PPS 信号,但我无法生成中断。

我甚至使用逻辑分析仪测试了此信号、方法是将其引导至 EVM 上的 SYNC_OUT0引脚。

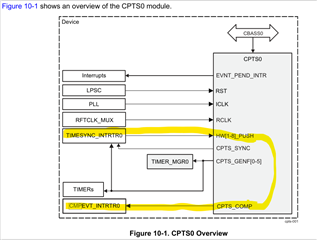

我还在 TRM 中应用了 CPTS 中断处理部分。

此致、金枪鱼 Girişken

您好、Tuna、

好的、这是我对你的系统的理解。 如果出什么问题、请告诉我:

Linux 正在控制 PRU 以太网。 您是否通过采用 PTP 的以太网获得了自己的时间?

您可以从 PRU 以太网生成 PPS 输出。 现在、您需要有关如何在内部发送 PPS 信号以便 R5F 内核可以接收 PPS 信号的更多指导。

此致、

Nick

您好、Tuna、

PPS 事件是否是比较事件? 由于我们甚至可以对其进行比较、因此我们也可以轻松地将此事件路由路由 到 CMP_EVEN_INTR 路由器、再到 A53内核或 R5F 内核。

此致、

Anil。

您好、Nick。

到目前为止、我只想确定部件。 我在 Linux 设备树中进行了更改

[报价 userid="561282" url="~/support/processors-group/processors/f/processors-forum/1366251/am6442-inter-core-time-sync-routing-between-a53-and-r5/5238349 #5238349"]如果我在 TIMESYNC_ROUTER 节点下的 Linux 设备树中进行如下更改、是否会自动生成中断?

&TIMESYNC_ROUTER{ pinctrl-names ="默认值";pinctrl-0 =<&icssg_cpts_pps>; /*时间同步路由示例*/ icssg_cpts_pps:icssg_cpts_pps{ PINCTL-SINGLE、PINS =< /* pps [pr1_edc0_sync0_out] in29 -> out16 [CPTS_HW1_PUSH]*/ TS_OFFSET (16、29) >; }; };

和

我设法生成了文档中所述的 PPS 信号( software-dl.ti.com/.../PRU_ICSSG_Ethernet.html )

之后、我预计 pps 信号将降至 MCU 回调中、如下所示:

尊敬的 Anil:

我不确定它是否是比较事件。

我设法生成了文档中所述的 PPS 信号( software-dl.ti.com/.../PRU_ICSSG_Ethernet.html )

我在文档中也看不到与此相关的内容。 但如果是、我应该怎么做才能将此事件路由到 R5F 内核?

此致、

金枪鱼 Girisken.

您好、Tuna、

根据上述文档、PPS 似乎不是 比较事件、这是同步事件、并且此事件不会路由到任何路由器。

[报价 userid="280115" url="~/support/processors-group/processors/f/processors-forum/1366251/am6442-inter-core-time-sync-routing-between-a53-and-r5/5243898 #5243898"]我可以从 Linux 的角度进行评论、但 Anil 是从"允许 R5F 内核接收信号"的角度进行评论的团队成员。

目前、我们没有可以向您介绍如何配置中断聚合器(IA)以将输入信号从时间同步路由器路由到 R5F 的示例。 我知道我们花了一些时间研究了如何编写一个示例、但我不知道我们已经深入到了代码开发和调试过程中。 我在问。

[报价]您能否确认金枪鱼正在尝试从上述时间同步架构向时间同步中断路由器提供哪个输入值?

因为 EDC 同步不会同步到任何路由器。

@ó n Tuna,

通常、任何路由器都可以通过 R5F 和 M4F 内核上的 SCL 客户端进行配置。

因此、您需要将什么是输入、什么是输出传递到 CMP 事件中断路由器。

接下来、我们需要向目标内核注册一个中断。

请查看下面的示例。 在本示例中、我们根据 IEP 计数器生成 DMA、并了解我们如何将比较事件路由到 CMP 事件 INT 路由器。

此致、

Anil。

您好、Tuna、

我设法生成了文档中所述的 PPS 信号( software-dl.ti.com/.../PRU_ICSSG_Ethernet.html )

根据上述内容、您提到了管理从 https://software-dl.ti.com/processor-sdk-linux-rt/esd/AM64X/latest/exports/docs/linux/PPS/PRU-ICSS/PPS/PRU_ICSS_ICSSG_Ethernet.html Foundational_Components?highlight = icssg#pps-pulse-per-second-support 生成信号 、其中所示示例显示来自 PRG0_IEP0_YNC_SYNC_OUT0 的 Linux_Drivers、并且不会通过时间同步路由器(即不会影响 EDC 中的时间同步节点)。

您如何验证 PPS 信号是否显示?

====================================================================================================

正如我在 https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1371026/am6442-how-to-generate-pps-from-pru-iep 中提到的、仅为了从 PRU ICSSG IEP 生成 PPS 信号、不需要时间同步路由器。 我不确定要路由到 R5内核、但根据这里的讨论、似乎需要时间同步路由器。

如果需要时间同步路由器、则您在 DTS 的&TIMESYNC_ROUTER 节点中进行的配置非常重要。 在您之前分享的以下片段中、您似乎正在将时间同步路由器的输入设置为时间同步中断 ID 29 (PRU_ICSSG1_PR1_EDC0_SYNC0_OUT_0)。 可在 TRM 表9-73 TIMESYNC_INTRTRTR0中断映射中检查该值。

另外、您似乎将来自时间同步路由器的输出设置为 Main CPTS HW push 1。

×ync_router {

pinctrl-names = "default";

pinctrl-0 = <&icssg_cpts_pps>;

/* Example of the timesync routing */

icssg_cpts_pps: icssg_cpts_pps {

pinctrl-single,pins = <

/* pps [pr1_edc0_sync0_out] in29 -> out16 [cpts_hw1_push] */

TS_OFFSET(16, 29)

>;

};

};

因此、您需要传递什么是输入、什么是输出、应该传递给 CMP 事件中断路由器。

利用来自 Anil 的这些信息、我猜测时间同步路由器的输出随后应该会传递到 CMP 事件中断路由器。 那么、我猜测下面的路径可能是这样的内容。 如果我错了、Swargam Anil 会纠正我。

-道林

您好、Tuna、

您好、Daolin

我们实施了 Daolin 所建议的方法(我们将主 CPTS 与来自 IEP 的 PPS 信号同步、然后针对我们的特定用例实施了更多)、但我相信还有一个更简单的解决方案。

可以通过 PRU 中断控制器从 ICSSG 导出 Sync0信号。 这就是 EtherCAT 子器件代码之类的功能。 它能够在 Sync0脉冲上生成 R5f 中断。

这样做的困难可能不会干扰 ICSSG 以太网的固件和 Linux 驱动程序、但这是可以实现的、并且这是一种更直接的方法。

此致、

Dominic

可通过 PRU 中断控制器从 ICSSG 导出 Sync0信号。 这就是 EtherCAT 子器件代码之类的功能。 它能够在 Sync0脉冲上生成 R5f 中断。[/QUOT]这就简单得多了。 SYNC0和 SYNC1可通过 PRU_ICSSGx_PR1_HOST_INTR_pend_y 路由到 R5F VIM 或 A53 GIC。 EtherCAT 子器件代码是一个很好的参考。

SYNC0通常通过 CMP1生成、SYNC1依赖于 SYNC0 (针对 EtherCAT)或独立于 PROFINET (对于 TI、通过 CMP1触发、对于 TO、通过 CMP2触发、每个周期通过 CMP0触发脉冲)。 因此、另一种选项是根据对应于 R5F 或 A53的 CMPx_HIT 事件通过映射到 PRU_ICSSGx_PR1_IEPy_CMP_INTR_REQ_0/1/2的 CMPEVT_INTRTR0输出生成中断

你好、Daolin

您如何验证 PPS 信号是否显示?

实际上、我无法验证它。 这就是我想要检查是否缺少什么的原因。 感谢 Swargam Anil 、我知道这是一个缺失的部分。

-金枪鱼 Girisken

您好、PratheeshGangadhar

感谢您和 Dominic 加入本主题。

是否可以与我分享一个 将 同步信号路由到 R5F 内核的示例?

此致、

金枪鱼 Girisken.

您好、Tuna、

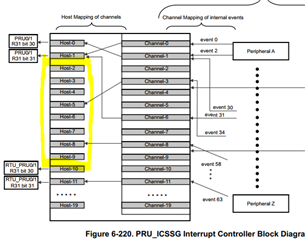

我的方法是使用 ICSSG 的 INTC 将 IEP 的 Sync0事件导出至 R5f:

主机中断2-9映射到器件级(即 R5f 和 A53)中断。 您必须检查 ICSSG 以太网固件/ Linux 驱动程序配置的通道和主机中断是否/哪些通道和主机中断、以及某些通道和主机中断未使用。

您可以查看工业通信 SDK 中的 EtherCAT 子器件源、了解如何配置此类中断、因为这正是 EtherCAT 子器件实施方案在 R5f 内核上获取 Sync0中断的方式。

我相信 Pratheesh 的方法看起来更简单。

如果查看 Linux 中的 ICSS_IEP.c 源代码、您会发现它将 CMP1配置为 PPS 输出。 只需通过 CMPEVT_INTRTRTR0设置一条从此处到 R5f 的路由:

这应该是可能的使用 Sciclient_rmIrqSet (),见 https://downloads.ti.com/tisci/esd/latest/5_soc_doc/am64x/interrupt_cfg.html#cmp-event-introuter0-interrupt-router-input-sources 和 https://downloads.ti.com/tisci/esd/latest/5_soc_doc/am64x/interrupt_cfg.html#cmp-event-introuter0-interrupt-router-output-destinations 的 输入和输出参数。

不确定是否需要在 IEP 寄存器中进行其他配置。

我没有现成的任何示例。 也许 TI 的相关人员可以帮助您解决这个问题。

此致、

Dominic

您好、Tuna、

[报价 userid="6980" url="~/support/processors-group/processors/f/processors-forum/1366251/am6442-inter-core-time-sync-routing-between-a53-and-r5/5251066 #5251066"]因此、另一个选项是基于对 R5F 或 A53的相应 CMPx_HIT 事件生成中断(通过映射到 PRU_ICSSGx_PR1_IEPy_CMP_INTR_REQ_0/1/2[/报价]的 CMPx_HIT 输出)根据上面的 Pratheesh 建议、同步0甚至已路由到 CMP1事件、我们不需要配置任何 IEP 寄存器将 CMP1事件路由到目标内核。

现在、将此事件路由到 R5F 内核、我们需要执行两个步骤。

1. 将 CMP 事件路由到 CMP 事件中断路由器

2.接下来、将比较中断路由到目标 R5F 内核。

根据 TRM、16至23个路由器输出连接到 R5F 内核、而将路由连接到软件时、只有16至19个路由器输出连接到目标内核。

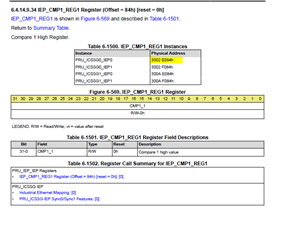

请查看下面的图片。

在下面的配置中、我已将 PRU 内核0 IEP0 CMP1事件路由到目标 R5F 内核。

您需要根据 PRU 内核和 IEP 修改此输入。 除此之外、所有这些应该都能正常工作。

如果您遇到任何问题、请告知我们。

/* Compare Interrupt */

#define CMPEVT_OFFSET (CSLR_CMP_EVENT_INTROUTER0_IN_PRU_ICSSG0_PR1_IEP0_CMP_INTR_REQ_1) /* CSLR_CMP_EVENT_INTROUTER0_IN_PRU_ICSSG1_PR1_IEP1_CMP_INTR_REQ_0 */

#define CMP_EVENT_ROUTER_OUT (16U)

#define CMP_EVENT_INT (CSLR_R5FSS0_CORE0_INTR_CMP_EVENT_INTROUTER0_OUTP_16) /* CSLR_R5FSS0_CORE0_INTR_CMP_EVENT_INTROUTER0_OUTP_16 */

#define CMPEVT_IN_CMP (8U + CMPEVT_OFFSET)

void configure_cmp_router_isr( void)

{

HwiP_Params cmp_hwiPrms;

HwiP_Object cmpHwiObject;

int32_t retVal;

struct tisci_msg_rm_irq_set_req rmIrqReq;

struct tisci_msg_rm_irq_set_resp rmIrqResp;

HwiP_Params_init( &cmp_hwiPrms );

cmp_hwiPrms.callback = &cmp_callabck_function;

cmp_hwiPrms.intNum = CMP_EVENT_INT;

cmp_hwiPrms.priority = 4U;

cmp_hwiPrms.isFIQ = 0U;

cmp_hwiPrms.isPulse = TRUE;

HwiP_construct( &cmpHwiObject, &cmp_hwiPrms );

rmIrqReq.valid_params = 0U;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_ID_VALID;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_HOST_IRQ_VALID;

rmIrqReq.global_event = 0U;

rmIrqReq.src_id = TISCI_DEV_CMP_EVENT_INTROUTER0;

rmIrqReq.src_index = CMPEVT_IN_CMP;

rmIrqReq.dst_id = TISCI_DEV_CMP_EVENT_INTROUTER0;

rmIrqReq.dst_host_irq = CMP_EVENT_ROUTER_OUT;

rmIrqReq.ia_id = 0U;

rmIrqReq.vint = 0U;

rmIrqReq.vint_status_bit_index = 0U;

rmIrqReq.secondary_host = TISCI_MSG_VALUE_RM_UNUSED_SECONDARY_HOST;

retVal = Sciclient_rmIrqSetRaw(&rmIrqReq, &rmIrqResp, SystemP_WAIT_FOREVER);

if(0 != retVal)

{

DebugP_log("[Error] Sciclient event config failed!!!\r\n");

DebugP_assert(FALSE);

}

return;

}

void cmp_callabck_function(void *args)

{

}此致、

Anil。

您好、Anıl

我上星期生病了,所以我不能尝试你说的,直到现在。

我已根据您共享的配置文件配置了我的 MCU 应用、并在回调函数(CMP_CALLABCK_FUNCTION)中添加了一个计数器、以便可以测试 pps 是否到达 R5F 内核。 但它不起作用。 我已将 CMPEVT_OFFSET icssg0更改为 icssg1、因为我在设备树中执行了 该操作

&TIMESYNC_ROUTER{

pinctrl-names ="默认值";

pinctrl-0 =<&icssg_cpts_pps>;

/*时间同步路由示例*/

icssg_cpts_pps:icssg_cpts_pps{

PINCTL-SINGLE、PINS =<

/* pps [pr1_edc0_sync0_out] in29 -> out16 [CPTS_HW1_PUSH]*/

TS_OFFSET (16、29)

>;

};

};

正如您在上图中看到的、in29对应于 icssg1.我 还在 Linux 设备树中的 in25而不是 in29和 MCU 端创建了与您的配置文件完全相同的内容、但这两者都不起作用。 您是否知道会出现什么问题?

顺便说一下、您提到了两个步骤。

[报价 userid="525901" url="~/support/processors-group/processors/f/processors-forum/1366251/am6442-inter-core-time-sync-routing-between-a53-and-r5/5254584 #5254584"]现在、将此事件路由到 R5F 内核、我们需要执行两个步骤。

1. 将 CMP 事件路由到 CMP 事件中断路由器

2.接下来、将比较中断路由到目标 R5F 内核。

[报价]我可以看到配置文件中的第二部分,但我无法理解您是如何"将 CMP 事件路由到 CMP 事件中断路由器 "的。 我缺失的器件可能是这个?

此致、

金枪鱼 Girisken.

您好、金枪鱼 Girisken

[报价 userid="525901" url="~/support/processors-group/processors/f/processors-forum/1366251/am6442-inter-core-time-sync-routing-between-a53-and-r5/5254584 #5254584"]如果您遇到任何问题、请告知我们。

[报价]以上代码工作正常。 只是,我已经配置了 CMP 计时器没有任何网络协议 ,并 在计数器达到 X 时间后验证,无论中断是否在 R5F 内核中。

这是很好的工作。

我可以在配置文件中看到第二部分、但我无法理解您是如何"将 CMP 事件路由到 CMP 事件中断路由器 "的。 可能我缺少的器件是这个?[/QUOT]在 AM64X 上、所有路由器配置都应通过 SCI 客户端完成。

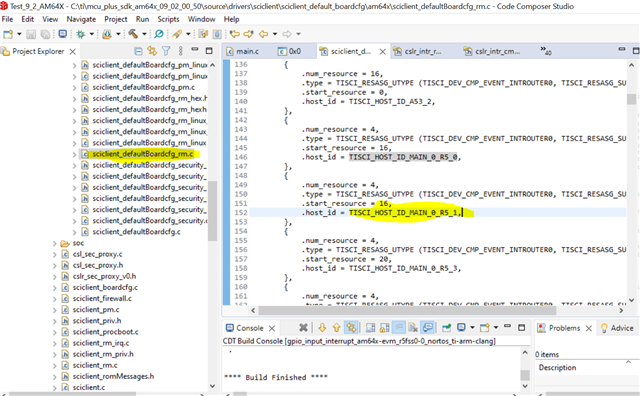

为此、我们需要配置4个参数、请查看下面的代码。

我们需要配置 CMP 事件中断路由器、以便我们需要传递 src 索引和 DST 主机 IRQ 值。

Fullscreen123456789rmIrqReq.src_id = TISCI_DEV_CMP_EVENT_INTROUTER0;rmIrqReq.src_index = CMPEVT_IN_CMP;rmIrqReq.dst_id = TISCI_DEV_CMP_EVENT_INTROUTER0;rmIrqReq.dst_host_irq = CMP_EVENT_ROUTER_OUT;XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXrmIrqReq.src_id = TISCI_DEV_CMP_EVENT_INTROUTER0; rmIrqReq.src_index = CMPEVT_IN_CMP; rmIrqReq.dst_id = TISCI_DEV_CMP_EVENT_INTROUTER0; rmIrqReq.dst_host_irq = CMP_EVENT_ROUTER_OUT;在当前示例中、我想将比较1事件路由到路由器、以便低于宏值的传递为 CSLR_CMP_EVENT_INTROUTER0_IN_PRU_ICSSG0_PR1_IEP0_CMP_INTR_REQ_1

另外、16到23的 CMP 路由器输出路由到 SoC 上的 R5F 内核、如下图所示。

16到20个路由器输出路由到目标内核。 因此、我使用了16作为路由器的输出。

如果上述参数错误,我们应该得到 SCI 客户端错误,似乎没有错误在您的工作台,这意味着这些参数已正确配置.

如果 CMP 1生成事件、则应将其路由到 具有上述更改的 R5F 内核。

如果不能解决,我们在 A53核心侧缺少一些东西,

PratheeshGangadhar Nick Saulnier 您能在这里帮助吗?

此致、

Anil。

您好!

过去几天、我尝试重现从 IEP 到 R5内核路由 CMP1事件的建议方法。 很遗憾,就像金枪鱼一样,我没能做到这一点。 我还尝试更改器件树节点并尝试使用 src_index 和 dst_host_IRQ 值、但没有成功。

如果确认 R5端代码在手动配置的 CMP 计时器下运行良好、那么您是否有任何建议来探讨 A53端该链中的哪个链路可能是问题? 是否有任何其他 CMP 事件(不一定来自 IEP) 默认 路由到 R5 并可用于测试中断?

此致、

Mateusz

尊敬的 Mateusz:

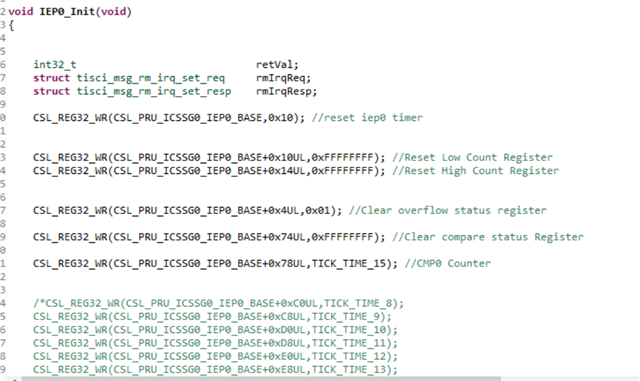

我已经尝试了下面的代码,在这种情况下,当 CMP 15 (PRU 内核0+IEP0 )到期到125usec 时,只验证中断是否会进入 R5F 内核每个125usec。 但是、这是有效的。

根据 Pratheesh 的提议、已 sync0事件将路由到 CMP1。

因此、在 A53侧、如果触发此 synch0事件并在 R5F 内核配置以下更改之后。

synch0事件应路由到目标内核 R5F。

如果任何事件未 ROOT 到目标内核、则 sysnc0事件不会 映射到 CMP 事件。

我不熟悉如何将 synch0与 CMP1事件链接。

我需要与网络专家核实这个主题,并将与您联系。

同时、我随附示例供您参考。

/* Register pin interrupt */

HwiP_Params_init(&hwiPrms);

hwiPrms.intNum = CSLR_R5FSS0_CORE0_INTR_CMP_EVENT_INTROUTER0_OUTP_17;

hwiPrms.priority = 4U;

hwiPrms.callback = &IepIsrFxn;

hwiPrms.isPulse = TRUE;

retVal = HwiP_construct(&cmpHwiObject, &hwiPrms);

DebugP_assert(retVal == SystemP_SUCCESS );

rmIrqReq.valid_params = 0U;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_ID_VALID;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_HOST_IRQ_VALID;

rmIrqReq.global_event = 0U;

rmIrqReq.src_id = TISCI_DEV_CMP_EVENT_INTROUTER0;

rmIrqReq.src_index = CSLR_CMP_EVENT_INTROUTER0_IN_PRU_ICSSG0_PR1_IEP0_CMP_INTR_REQ_1;

rmIrqReq.dst_id = TISCI_DEV_CMP_EVENT_INTROUTER0;

rmIrqReq.dst_host_irq = 17U;

rmIrqReq.ia_id = 0U;

rmIrqReq.vint = 0U;

rmIrqReq.vint_status_bit_index = 0U;

rmIrqReq.secondary_host = TISCI_MSG_VALUE_RM_UNUSED_SECONDARY_HOST;

retVal = Sciclient_rmIrqSetRaw(&rmIrqReq, &rmIrqResp, SystemP_WAIT_FOREVER);

if(0 != retVal)

{

DebugP_log("[Error] Sciclient event config failed!!!\r\n");

DebugP_assert(FALSE);

}

此致、

Anil。

我找到重新测试所附代码的时间、但仍然没有成功。 如果确认工作正常、则将 Sync0事件路由到 A53侧的 CMP1似乎存在问题。 网络专家是否有关于此器件的任何新闻?[/QUOT]尊敬的 Mateusz:

感谢您的确认。

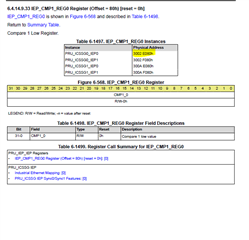

您能否确认 A53上是否启用了以下位?

如果没有、请启用、然后查看这是否起作用。

此致、

Anil。

Anil、您好!

我使用 devmem 检查了所有 IEP 实例的值、而这些位已针对 ICSSG0_IEP0启用、因此看起来配置正常。

# devmem 0x3002E180 0x00000003 # devmem 0x3002F180 0x00000000 # devmem 0x300AE180 0x00000000 # devmem 0x300AF180 0x00000000

尊敬的 Mateusz:

生成 PPS 中断不应需要对 ICSSG0_IEP0寄存器执行的所有操作 、因为此 IEP 应由 Linux 驱动程序控制、正确吗?

是的、您在我的测试代码中回答正确、我在控制 IEP 寄存器 、您不需要这些寄存器。

所以、在我的测试代码注释行从150到181中、之后编译项目并加载.out 文件。

请分享测试结果。

L

此致、

Anil。

Anil、您好!

今天、我成功构建并运行了随附的代码、但做了一些修改。 我可以确认 R5实际上是每1ms 接收一次中断、而没有在 IEP0_Init 中配置 ICSSG0_IEP0寄存器。 我将相同的配置代码复制到了 FreeRTOS 应用程序、但没有收到中断、但这在我们的 R5应用程序端肯定是一些配置错误、所以我会稍后尝试解决。

奇怪的是、1ms 的周期。 如果我理解正确、CMP1事件的频率由 IEP_CMP1_REG0/1寄存器中的值控制、这似乎是在 Linux 端的 ICSS_IEP.c 中完成的、但之后转换为寄存器值的时间结构值为1s -那么 CMP1事件周期是否也应该为1s?

此致、

Mateusz

今天我成功构建并运行了附带的代码并进行了一些修改。 我可以确认 R5实际上是每1ms 接收一次中断、而没有在 IEP0_Init 中配置 ICSSG0_IEP0寄存器。[/QUOT]尊敬的 Mateusz:

我假设仅由于 Linux 端的 IEP 寄存器初始化而触发该1ms 中断。

因为我们已经评论了 FreeRTOS 应用程序中的 IEP 寄存器初始化。

此致、

Anil。

Anil、您好!

我假设仅由于 Linux 端的 IEP 寄存器初始化而触发此1ms 中断。

正确- IEP 寄存器仅在 Linux 端初始化、R5端的配置被注释(因此不在 R5端的 IEP0_Init 上配置 ICSSG0_IEP0寄存器)。 但是、1ms 周期似乎仍然不清楚、因为当我检查 Linux 驱动程序源代码(ICSS_IEP.c)时、周期值似乎设置为1、然后以某种方式转换并写入 IEP 寄存器、因此根据我的理解、CMP1事件周期是指1、对吗?

下面是 ICSS_IEP.c 中的部分代码、这些代码可以让我通过这种方式理解它:

static int icss_iep_pps_enable(struct icss_iep *iep, int on)

{

// ...

ns = icss_iep_gettime(iep, NULL);

ts = ns_to_timespec64(ns);

rq.perout.period.sec = 1;

rq.perout.period.nsec = 0;

rq.perout.start.sec = ts.tv_sec + 2;

rq.perout.start.nsec = 0;

ret = icss_iep_perout_enable_hw(iep, &rq.perout, on);

// ...

}static int icss_iep_perout_enable_hw(struct icss_iep *iep,

struct ptp_perout_request *req, int on)

{

int ret;

u64 cmp;

// ...

// here values set in icss_iep_pps_enable are converted and written to u64 cmp

ret = iep->ops->perout_enable(iep->clockops_data, req, on, &cmp);

// ...

regmap_write(iep->map, ICSS_IEP_CMP1_REG0, lower_32_bits(cmp));

if (iep->plat_data->flags & ICSS_IEP_64BIT_COUNTER_SUPPORT)

regmap_write(iep->map, ICSS_IEP_CMP1_REG1, upper_32_bits(cmp));

/* Configure SYNC, 1ms pulse width */

regmap_write(iep->map, ICSS_IEP_SYNC_PWIDTH_REG, 1000000);

regmap_write(iep->map, ICSS_IEP_SYNC0_PERIOD_REG, 0);

regmap_write(iep->map, ICSS_IEP_SYNC_START_REG, 0);

regmap_write(iep->map, ICSS_IEP_SYNC_CTRL_REG, 0); /* one-shot mode */

/* Enable CMP 1 */

regmap_update_bits(iep->map, ICSS_IEP_CMP_CFG_REG,

IEP_CMP_CFG_CMP_EN(1), IEP_CMP_CFG_CMP_EN(1));

// ...

}尊敬的 Mateusz:

我不熟悉 Linux 方面、主要从事 RTOS/NORTOS 方面的工作。

但是、我在这里尽量帮助您、而不是检查上面的代码。

请分享下面 IEP 寄存器的寄存器转储、以便我们可以确认1ms 中断的来源。

A53侧 PRU 内核和 IEP 计时器的运行频率是多少?

此致、

Anil。

Anil、您好!

下面是来自寄存器的值:

# devmem 0x3002e000 0x00000841 # devmem 0x3002e070 0x00021807 # devmem 0x3002e080 0x00001388 # devmem 0x3002e084 0x00001388

enable prepare protect duty hardware

clock count count count rate accuracy phase cycle enable

-------------------------------------------------------------------------------------------------------

...

clk:81:20 0 0 0 250000000 0 0 50000 Y

30000000.icssg.coreclk-mux 0 0 0 250000000 0 0 50000 Y

30000000.icssg.iepclk-mux 0 0 0 250000000 0 0 50000 Y

...尊敬的 Mateusz:

请在触发1ms 中断的测试用例中确认、在此测试代码中、您将路由 CMP0或 CMP1吗?

是否修改了 SCI 客户端配置?

您是否还可以共享 CMP0寄存器值?

我无法弄清为什么1毫秒中断会伴随 CMP1来、因为 CMP1有很大的值。

根据上述信息,IEP 计数器1在 CMP1计数器的低值和高值时过期,该值不是1毫秒,而此 CMP1过期值是较大值。

我正在将此查询路由到右专家来评论这个问题。

此致、

Anil。

Anil、您好!

请在触发1ms 中断的测试用例中确认、在此测试代码中、您将路由 CMP0或 CMP1?

我将使用 CSLR_CMP_EVENT_INTROUTER0_IN_PRU_ICSSG0_PR1_IEP0_CMP_INTR_REQ_1路由 CMP1、这与您之前附加的代码相同。

您是否修改了 SCI 客户端配置?

否、我仅注释了 IEP0_Init 中的第150-181行、并更改了 syscfg 文件中的存储器区域、SCI 客户端配置是相同的。

您能否同时分享 CMP0寄存器值?

# devmem 0x3002e078 0x000F423C # devmem 0x3002e07C 0x000F423C

# devmem 0x3002e070 32 0x00021807 // disable CMP1 event - no interrupts # devmem 0x3002e070 32 0x00021803 // update CMP1_REG0 # devmem 0x3002e080 32 0x000C0000 // update CMP1_REG1 # devmem 0x3002e084 32 0x000C0000 // enable CMP1 event - interrupts triggering # devmem 0x3002e070 32 0x00021807