工具与软件:

您好!

我正在寻找一种 只使用 RBL 而不使用 IBL 引导 App.bin 的方法。

我在此主题下找到了一个回复:TMS320C6678:从 SPI 引导或在评估板上仅使用 RBL -处理器论坛-处理器- TI E2E 支持论坛、 但找 不到下面的链接! 我可以从哪里获得它?

或者我可以关注其他任何维基吗? 在如何将 CCS 输出文件 app.out 转换为 SPI-NORFlash 可启动格式时只使用 RBL 时、我感到困惑。

祝你一切顺利!

谢谢你

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我正在寻找一种 只使用 RBL 而不使用 IBL 引导 App.bin 的方法。

我在此主题下找到了一个回复:TMS320C6678:从 SPI 引导或在评估板上仅使用 RBL -处理器论坛-处理器- TI E2E 支持论坛、 但找 不到下面的链接! 我可以从哪里获得它?

或者我可以关注其他任何维基吗? 在如何将 CCS 输出文件 app.out 转换为 SPI-NORFlash 可启动格式时只使用 RBL 时、我感到困惑。

祝你一切顺利!

谢谢你

我正在寻找一种 只使用 RBL 引导 App.bin 而不使用 IBL 的方法。

请使用此链接:- [常见问题解答] TMS320C6657:如何在不使用 IBL 的 TI-C6657-EVM 上运行直接 SPI-boot 示例? -处理器论坛-处理器- TI E2E 支持论坛

请注意:-使用此链接获取您要求的转换方法。

给出的源代码用于 C6657器件、而不是 C6678。

——

您提到的 wiki 很久以前就没有调试了。

https://www.ti.com/lit/an/spracn2/spracn2.pdf -- Keystone 引导加载程序和资源----这与你上面提到的 wiki 相同。

可以、给出的"C6678_directrom_boot_examples.zip"链接会导航到某个错误的地址。

让我来尝试一下(因为不再有 Wiki 了、所以我对获得这个特定源代码没有信心)。

目前、您可以使用 C6657的源代码并为 C6678修改它。

此致

Shankari G.

谢谢。

由于我找不到 C6678的 C6678_directrom_boot_examples.zip 、我使用了 您提供给我的0435.C6657_directROM_Boot_example.zip。

但有一些问题:

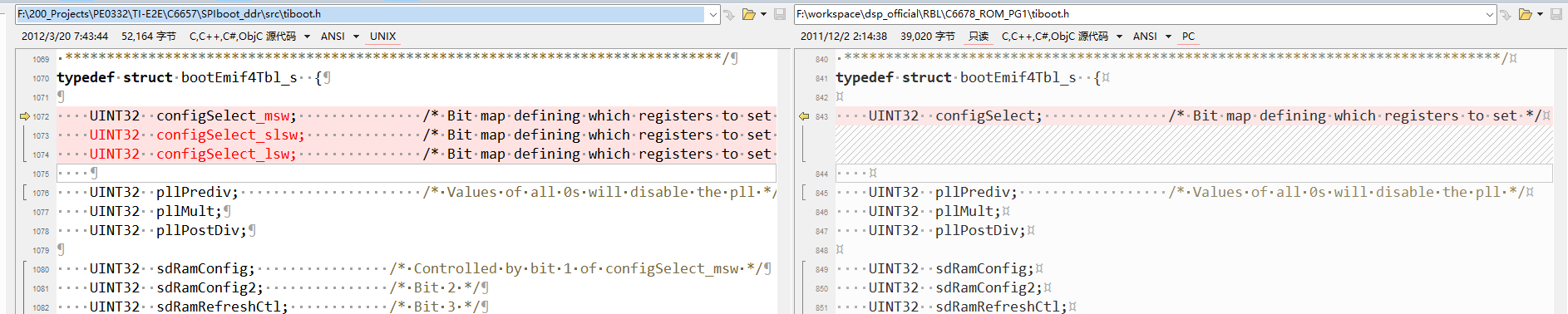

1. BootEmif4Tbl_s 示例中定义的与 RBL (C6678)不同、C6678的 RBL 是否会导致引导加载程序示例的映像出现问题?

值" emif4Cfg " C6657的示例中的 spiboot.c 中不适合与 C6678一起使用、您是否找到了 C6678_directROM_boot_examples.zip?我认为会好得多。

#pragma DATA_SECTION (emif4Cfg, ".emif4Cfg")

const BOOT_EMIF4_TBL_T emif4Cfg = {

BOOT_EMIF4_ENABLE_MSW_pllCtl | \

BOOT_EMIF4_ENABLE_MSW_sdRamTiming1 | \

BOOT_EMIF4_ENABLE_MSW_sdRamTiming2 | \

BOOT_EMIF4_ENABLE_MSW_sdRamTiming3 | \

BOOT_EMIF4_ENABLE_MSW_ddrPhyCtl1 | \

BOOT_EMIF4_ENABLE_MSW_sdRamRefreshCtl | \

BOOT_EMIF4_ENABLE_MSW_sdRamOutImpdedCalCfg | \

BOOT_EMIF4_ENABLE_MSW_sdRamConfig,

BOOT_EMIF_ENABLE_SLSW_config0 | \

BOOT_EMIF_ENABLE_SLSW_config6 | \

BOOT_EMIF_ENABLE_SLSW_config7 | \

BOOT_EMIF_ENABLE_SLSW_config8 | \

BOOT_EMIF_ENABLE_SLSW_config9 | \

BOOT_EMIF_ENABLE_SLSW_config10 | \

BOOT_EMIF_ENABLE_SLSW_config18 | \

BOOT_EMIF_ENABLE_SLSW_config19 | \

BOOT_EMIF_ENABLE_SLSW_config20 | \

BOOT_EMIF_ENABLE_SLSW_config22 | \

BOOT_EMIF_ENABLE_SLSW_config12 | \

BOOT_EMIF_ENABLE_SLSW_config23 | \

BOOT_EMIF_ENABLE_SLSW_config21, /* Config select slsw */

0, /* Config select lsw */

3, /* pllPrediv */

40, /* pllMult */

2, /* pllPostDiv */

0x62477AB2, /* sdRamConfig */

0, /* sdRamConfig2, dont care*/

0x0000144F, /* sdRamRefreshCtl */

0x1333780C, /* sdRamTiming1 */

0x30717FE3, /* sdRamTiming2 */

0x559F86AF, /* sdRamTiming3 */

0, /* lpDdrNvmTiming, dont care */

0, /* powerManageCtl, dont care */

0, /* iODFTTestLogic, dont care */

0, /* performCountCfg, dont care */

0, /* performCountMstRegSel, dont care */

0, /* readIdleCtl, dont care */

0, /* sysVbusmIntEnSet, dont care */

0x70074c1f, /* sdRamOutImpdedCalCfg, dont care */

0, /* tempAlterCfg, dont care */

0x0010010F, /* ddrPhyCtl1 */

0, /* ddrPhyCtl2, dont care */

0, /* priClassSvceMap, dont care */

0, /* mstId2ClsSvce1Map, dont care */

0, /* mstId2ClsSvce2Map, dont care */

0, /* eccCtl, dont care */

0, /* eccRange1, dont care */

0, /* eccRange2, dont care */

0, /* rdWrtExcThresh, dont care */

0x87A0047F, 0, 0, 0, 0, 0, 0x33, 0x3A,

0x2C, 0x2C, 0x21, 0, 0xAF00002, 0, 0, 0,

0, 0, 0xB7, 0xB1, 0xA4, 0xA4, 0x98, 0x200,

0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0

};

2. emif4表 在 C6678的 RBL 源代码中定义、该代码位于 ".ddr3表" 。 C6678_ROM_PG1\main\mainemif4cfg.c、但我找不到 RBL 中定义的".ddr3Table"位置以及 它的目标地址是什么。

#pragma DATA_SECTION (emif4Table, ".ddr3Table") #pragma DATA_ALIGN (emif4Table, 4) BOOT_EMIF4_TBL_T emif4Table;

3.我想跟踪 RBL 运行状态,根据他人的指南,我们可以加载符号到器件,并使用硬件断点来跟踪它。 我的问题是:如何编译和构建 RBL,符号文件是什么? 我可以使用哪些构建的符号文件?

再次感谢!

我在这里找到了 C6678的示例:TMS320C6678 :C6678 EVM SPI 引导示例(没有 IBL)的源码-处理器论坛-处理器- E2E 设计支持

如何编译和构建 RBL、

RBL 仅供我们参考。

(RBL 表示 ROM 引导加载程序。 它不会被用户/客户更改。)

它无法重新编译/构建。

此致

Shankari G.

如果无法编译/构建 RBL、 如何获取符号文件? 我想跟踪 RBL 运行状态。

下面是来自 7357的 wiki。Debugging Boot Issues.zip 互从 TMS320C6678获得:SPI boot 处理器论坛-失败-处理器- E2E 设计支持(TI.com)

川旭

从此处下载 ROM 引导源。

https://software-dl.ti.com/sdoemb/sdoemb_public_sw/rbl/1_0_C6678/index_FDS.html

——

此图片适用于 用户用来加载到 EEPROM 或 NOR/NAND 中的 IBL (中间引导加载程序)或次级引导加载程序。

此图片不适用于 RBL。

——

有关 IBL 的更多信息、请参阅此常见问题解答:-

——

此致

Shankari G.

非常感谢。

现在,我只能通过内部寄存器 和 L2SRAM 中的记录跟踪 RBL ,根据数据表 中的"2.4引导加载程序部分在 L2 SRAM"章节。

然后、我按照 C6678_directROM_boot_examples.zip 指南的说明、重建 led_play 工程、并使用 spi_boot.bat 创建 app.dat、并写入 SPI-NOR 闪存。 但在 POR 之后、它仍然无法正常工作。

从"引导日志"(0x00873200)和 RBL 源代码中、我发现了这一点 RBL 在"bootMainSpi"的循环中运行。

引导日志寄存器信息如下:

在"引导日志"信息中、有10条此格式的日志记录:

typedef struct bootLogEntry_s {

void *fileName; /* Pointer to a string containing the name of the file which is logging */

UINT32 line; /* The log line number */

SINT32 logCode; /* The log code */

} bootLogEntry_t;

因此、我认为图像格式可能不正确、我曾尝试检查文件格式是否错误、但我没有找到任何有关 cl6x/Hex6x/b2i2c/b2ccs/romparse 创建的文件格式的文档... 新功能。

sprui03b-Assembly Language Tools-v8.2.x.pdf 中似乎没有文件格式的说明。

您好、我已经检查了由中的源代码构建的 led_play.out 的格式 C6678_directROM_boot_examples.zip 是的。

然后、根据 C6678_SPIboot_usersManual.pdf、 编译后,我们必须运行 C6678\spiboot\build\spiboot.bat。

在 spiboot\build\spiboot.bat、中有几个步骤:

我理解第1、2、4、5节。

但我不明白的意思 第3部分:b2ccs . 我的皇后:

顺便说一下、由于我的硼业上没有 I2C-EERPROM、因此我不会使用 writer\NOR\evmc66xxl\bin 工具将 final app.dat 刻录到 SPI NORFlash 中、而是编写了一个单个 spi-writer 项目来完成这项工作。 以下是该项目的功能:

问题1:这样可以吗?

问题2:在 C:\ti\pdk_C6678_1_2_6\packages\ti\platform\evmc6678l\platform_lib\SPI 中、我发现默认的 NorFlash 只 支持 platform_devID_NORN25Q128、但我正在使用其他芯片、我的问题是:src 支持其他类型的芯片?

顺便说一下、由于我的硼业上没有 I2C-EERPROM、因此我不会使用 writer\NOR\evmc66xxl\bin 工具将 final app.dat 刻录到 SPI NORFlash 中、而是编写了一个单个 spi-writer 项目来完成这项工作。 以下是该项目的功能:

问题1:这样可以吗?

[报价]有。 没关系。

Q2:从 C:\ti\pdk_C6678_1_2_6\packages\ti\platform\evmc6678l\platform_lib\SPI 中找到了默认 src、 但我要使用的是其他芯片类型[我的问题]是的、RBL 也支持其他芯片。

(RBL 会初始化所有接口。 外设驱动程序将驻留在 RBL 上方的软件层中。 因此、默认情况下、它应支持所有兼容的 NOR 芯片设备。。。)

平台支持库中提供了一个支持 NORN25Q128器件的示例。 用户可以修改平台库源文件以包含其 NOR 器件。

此平台库仅供客户使用。 可以对其进行编译和重建。

若要重新构建平台库、请执行此处给出的步骤:-

==================================================

[常见问题解答] TMS320C6657:如何解决 Processor SDK 6.3中 PDK 平台测试示例中的 CSL 错误? -处理器论坛-处理器- TI E2E 支持论坛

[常见问题解答] TMS320C6657:如何在 Processor SDK 6.3中解决 PDK 平台测试示例中的错误错误? -处理器论坛-处理器- TI E2E 支持论坛

此致

Shankari G.

非常感谢。

现在、我可以在之后引导 led_play 项目目标文件 0647.C6678_directROM_boot_examples.zip。 当然,我做了一些努力:

nysh.spi.map: 。 "SW_PLL_prediv"、"SW_PLL_mult"、 它在海关板上工作正常、我们的 LED 驱动正常。

section {

boot_mode = 50

param_index = 0

options = 1

core_freq_mhz = 1000

exe_file = "led_play.i2c.ccs"

next_dev_addr_ext = 0x0

sw_pll_prediv = 0

- sw_pll_prediv = 5

- sw_pll_mult = 32

+ sw_pll_prediv = 0

+ sw_pll_mult = 19

sw_pll_flags = 1

addr_width = 24

n_pins = 4

csel = 0

mode = 0

c2t_delay = 0

bus_freq_mhz = 0

bus_freq_khz = 500

}

但是、这里有一个新问题。 由于 我们的定制电路板上没有 I2C-EEPROM、并且我们应用程序的部分过大、因此我们必须将其中一部分放入 DDR 中。 因此、在引导加载程序将 DDR3移至 DDR 存储器之前、我们必须先初始化 DDR3。

我想可以通过3种方法来处理它。

每种方法都有一些问题:

Q1关于方法1:

POR 后、我发现配置为最目标寄存器、但 DDR 仍然不稳定。 然后我发现主 PLL 寄存器值 与 excuted GEL 文件中的寄存器值不同。 如何使用.emif4Cfg 表设置主 PLL? 以下参数是否有效?

0, /* pllPrediv */

7, /* pllMult */

0, /* pllPostDiv */

在 C6678的数据表中、可以对 CLK 进行计算:CLK = CLKIN×((PLLM+1)÷((OUTPUT_Divid+1)×(PLLD+1)))

PLLM-->pllMul?

PLLD--> pllPostDiv?

output_divide-->?

CLKIN-->? (我们的定制电路板是100MHz、但是 RBL 如何获得该值?)

Q2关于方法2:

如何创建引导 配置表并将其添加到烧录目标文件中?

Q3关于方法3:

由于我们的应用目标文件被写入了 SPI-FLASH、所以我们必须从 SPI-NOR 闪存引导它、组件文件中是否有演示?

此致

Chuan Xu

是的、谢谢。

这是解决我的问题的最后一种方法:

EVM6678LE I2C-NOR 闪存引导的具体操作问题 SPI 闪存引导处理器论坛-处理器- 设计支持- E2E 与(TI.com)