工具与软件:

尊敬的 Expert:

我的客户报告了有关 TPS6593断电序列问题的问题、

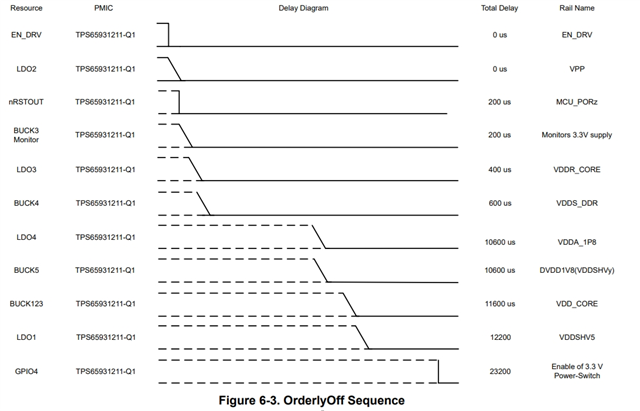

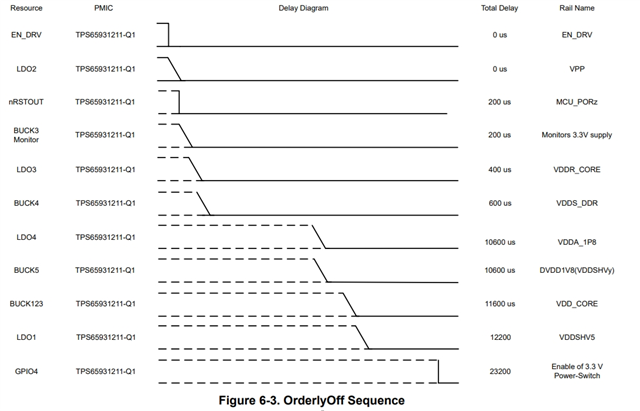

之前 NVM 修改为0x0、断电序列遵循如下(OrderlyOff)。

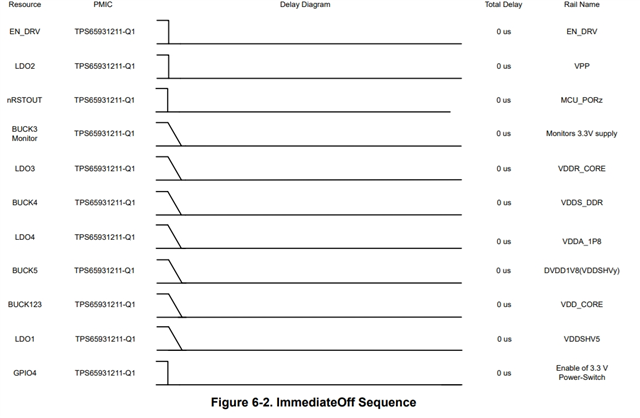

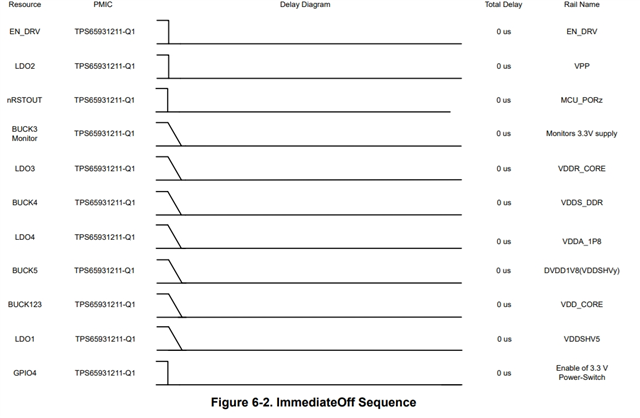

新的 PMIC NVM 修订版本现在更改为0x05。 且断电序列会更改为 immediateOff、同时断电。 您能帮助解决这个问题吗? 对 AM62A 有影响吗?

Biao

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的 Expert:

我的客户报告了有关 TPS6593断电序列问题的问题、

之前 NVM 修改为0x0、断电序列遵循如下(OrderlyOff)。

新的 PMIC NVM 修订版本现在更改为0x05。 且断电序列会更改为 immediateOff、同时断电。 您能帮助解决这个问题吗? 对 AM62A 有影响吗?

Biao

您好????、Biao、

我假设右侧示波器的差值大约为1.2ms。

这是两个不同的项目、所以两个不同的板、但使用相同的关断方法。

现在、虽然我们可以重点讨论硬件差异、但我认为最好看看关断方法。 如果在故障后可以读回 I2C 总线上的 PMIC、中断(寄存器:0x5A - 0x6C)将确认我认为真实的情况。

在涉及 PMIC 编程的代码中、我指出无论版本如何、关断源都是相同的。 从示波器左侧显示的所有电压轨(BUCK123 (VDD_CORE)、LDO3 (VDDR_CORE)和 BUCK4 (VDDS_DDR))的时间戳到屏幕直接显示的右侧电压轨、左侧的所有电压轨立即关闭、这表示立即关断、因为 VDD_CORE 和 VDDR_CORE 通常相差10ms。 右侧的差值为1.2ms、因此问题是、它来自哪里?

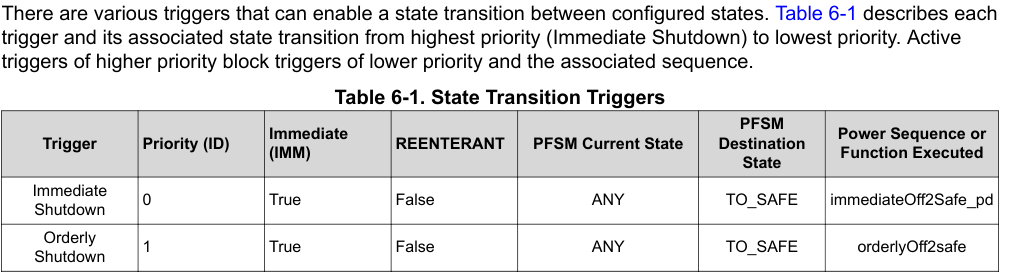

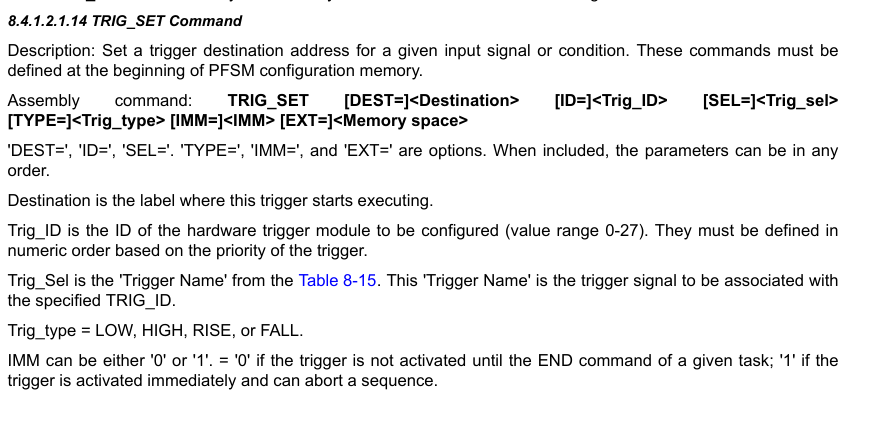

右侧发生的情况可能是有序关断、该情况在有序期间立即关断、因此 VDD_CORE 和[VDDR_CORE_VDDS_DDR]之间存在1.2ms 的差异。 由于即时关断的优先级取代了有序关断并可以中断。 请参阅以下触发优先级列表和 TRIG_SET 命令中的立即设置。

此致、

尼古拉斯·麦克纳马拉