主题中讨论的其他器件:SysConfig

工具与软件:

你(们)好

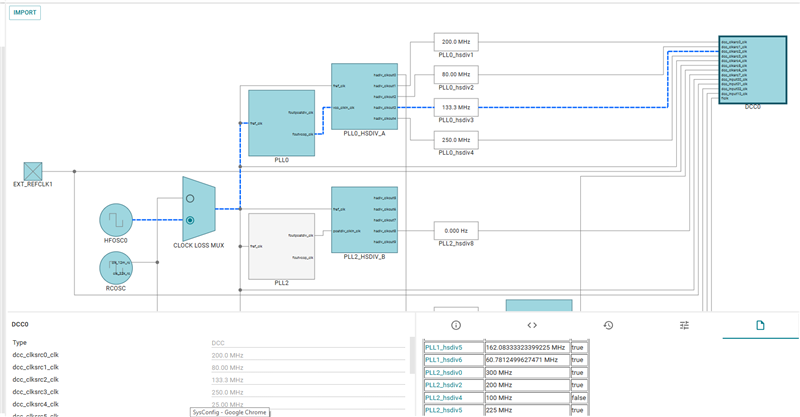

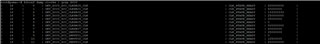

在在 AM6642的 R5内核上运行的应用中、我们要使用 DCC 外设来监控一些系统时钟。 首先、我想检查特定 DCC 时钟源的确切频率是多少-为此目的、我使用了 k3conf 工具。 我不清楚 k3conf 输出与 用户指南中写入的内容之间的比较情况

首先我要检查可用于 DCC0实例的时钟源

2. 在表12-4790的用户指南中、我看到 DCC0的时钟源0是 MAIN_PLL0_HSDIV1_CLKOUT、因此我想验证 上面显示的时钟源0频率是否与 MAIN_PLL0_HSDIV1_CLKOUT 的频率相匹配

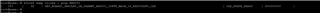

3.从1)我看到时钟源0的频率应该为 200000000 Hz、因此我通过短语 HSDIV1来执行 grep 操作。 结果表明、HSDIV1的频率与 DEV_DCC0_DCC_CLKSRC0_CLK 不匹配

所以是电路板上配置有误、还是我从 k3conf 工具和用户指南中的信息解码有误?

BR

雅库布