主题中讨论的其他器件:SysConfig

工具与软件:

如前所述、我们按照图2-1连接了我们的器件:AM62Ax/AM62Px LPDDR4电路板设计和布局布线指南

该存储器器件是双芯片、但每个芯片只有一个芯片选择、即 CS_A 和 CA_B

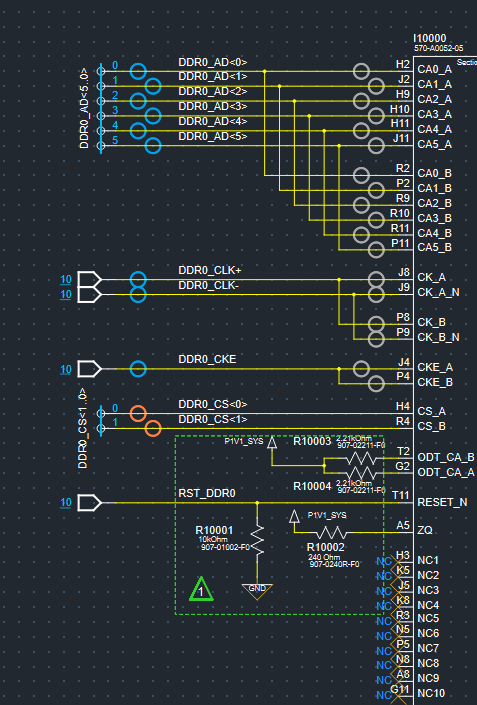

我们的原理图中的内存侧如下:

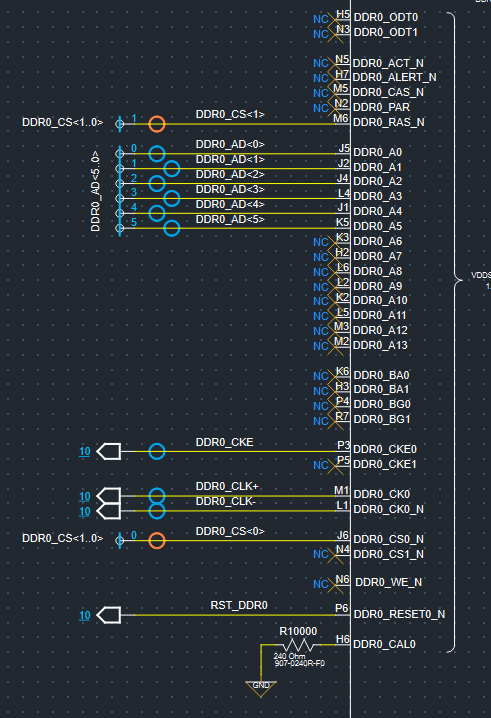

下面是处理器方面:

实质上:

DDR0_CS0_N -> CS_A

DDR0_RAS_N -> CS_B

我担心的是同一图的注释[1]表明处理器在这两个引脚上生成相同的信号、这似乎与南亚的说法不兼容、该说法是"我们的数据表是为 NT6AN256T32AC-J2H 封装内每个 x16的单独信号定义的"。

我们的问题是:

- 这是此存储器设备的正确接线配置吗?

- 如果是、正确的配置命名规则是什么(例如双通道单列)?

- 如果不包含:

- 正确的布线配置和命名规则是什么?

- 我们可以如何利用这些板上的功能、应该如何配置它?

我们可以根据需要对 PCB 进行一些返工、使它们进入可操作状态。