Thread 中讨论的其他器件:66AK2H14

工具与软件:

您好!

我阅读了 SPRSP79B 数据表文档和 SPRUJ52C TRM 文档。

我对 bootmode 和 MCU_bootmode 有几个问题:

- 表4-5指的是 POST 功能、但我找不到每个功能所涉及的描述

- 帖子造成的延迟是什么?

- 如何利用 POST 结果? 是否有一个默认的"输出控制台"给出结果(例如 UART ?) . 它们是否只能通过 JTAG 查看?

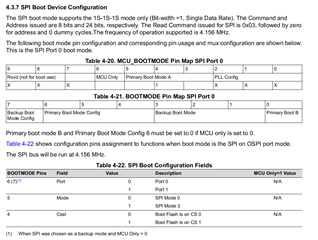

- 当 MCU_ONLY=0时、我们可以在表4-10中找到一些 QSPI 引导配置: "PRIMAY boot mode config (6..4)" (解释为"PORT / RSVD/CSEL")、表4-17详细介绍了端口和 CSEL、但我们不知道 RSVD 的值是多少。 这是不是"不关心"? 或者我们应该强制引脚为"0"吗? 或"1"?

- 在 考虑 SPI 引导(因此 MCU_ONLY=0且 Primary_BOOT_MODE_B_PIN=1)时、我们可以参考表4-11、但未提供所需的"BACKUP_BOOT_MODE_CONFIG"值

=> 是不是"关心"? 或者我们应该强制引脚为"0"吗? 或"1"?

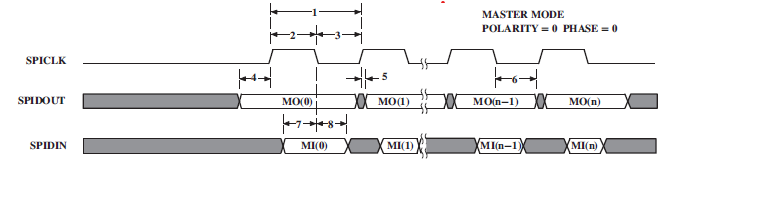

- 考虑 SPI 引导表4-22时、提供了模式0和模式3之间的可能选择、但我找不到任何解释每种模式的同步图

- 哪一个是激活数据输出的 SPI 时钟边沿:上升? 还是下降?

- 哪个是 SPI 时钟边沿捕获数据输入:上升? 还是下降?

数据表给出了一些开关特性(图6-98至6-103)、但 t 不十分清楚哪些适用于模式0、哪些适用于模式3。 您能解释更多吗?

- 考虑 SPI 引导时、我们可以在表4-1中看到、提及的 SOC 外设唯一一个是 MCU_FSS0_OSPI0。 但是、我们可以在表4-22中发现、可以选择 PORT0或端口1。 您是否确认 Port1是否对应于 MCU_FSS0_OSPI1? 因此、表4-1中应提到哪些? 还是混合物?

- 考虑 PCIe 引导表4-10和表4-46时、给出了一些可能的配置、例如保留/SSC/时钟

- 你能解释什么应该是保留值:"不用考虑? 0? 或1?

- 表4-46对"南南合作"没有任何解释。 在这种情况下、我们应该得出什么结论? 通过 PCIe 引导时、SSC 始终默认激活? 还是始终停用?

- 关于"计时":

- 外部引脚的含义是什么? 您是否确认它是指 SERDESx_REFCLK (典型的100 MHz 频率)、其中"x"是 SERDES 的编号?

- 内部时钟的含义是什么? 您是否建议 PCIe 时钟可以由内部 PLL 阐述? 在这种情况下、由于其他 PCIe 端点应该接收外部时钟、因此只能用于根端口? 不是吗?

感谢你的帮助

此致、

Bruno