主题中讨论的其他器件:AM62A7、 AM62A3、SK-AM62A-LP

工具与软件:

尊敬的专家

我们有以下链接中的相同问题。

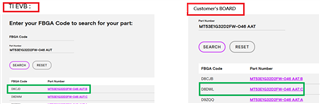

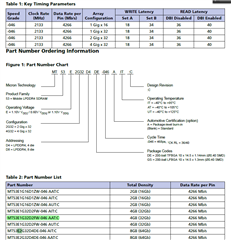

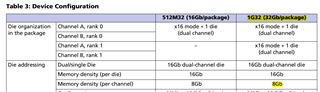

这是定制电路板、DDR 芯片与 AM62A EVM (MT53E1G32D2FW)、SDK10.0、SD 引导相同

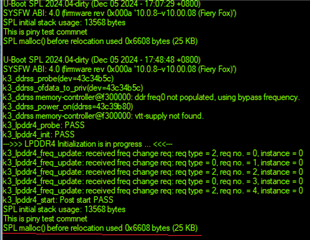

然后、我们尝试添加调试信息、如下所示。

似乎通过了 DDR 探针测试、但在 SPL malloc 测试中失败

我们使用同一 SD 卡进行 AM62A EVM 引导。 按如下方式进行记录

U-Boot SPL 2024.04-dirty (Dec 05 2024 - 17:48:48 +0800) SYSFW ABI: 4.0 (firmware rev 0x000a '10.0.8--v10.00.08 (Fiery Fox)') k3_ddrss_probe(dev=43c34b5c) k3_ddrss_ofdata_to_priv(dev=43c34b5c) k3_ddrss memory-controller@f300000: ddr freq0 not populated, using bypass frequency. k3_ddrss_power_on(ddrss=43c39b80) k3_ddrss memory-controller@f300000: vtt-supply not found. k3_lpddr4_probe: PASS k3_lpddr4_init: PASS --->>> LPDDR4 Initialization is in progress ... <<<--- k3_lpddr4_freq_update: received freq change req: req type = 2, req no. = 0, instance = 0 k3_lpddr4_freq_update: received freq change req: req type = 0, req no. = 1, instance = 0 k3_lpddr4_freq_update: received freq change req: req type = 2, req no. = 2, instance = 0 k3_lpddr4_freq_update: received freq change req: req type = 0, req no. = 3, instance = 0 k3_lpddr4_freq_update: received freq change req: req type = 2, req no. = 4, instance = 0 k3_lpddr4_start: Post start PASS SPL initial stack usage: 13568 bytes This is piny test commnet SPL malloc() before relocation used 0x6608 bytes (25 KB) >>SPL: board_init_r() spl_init Trying to boot from MMC2 Authentication passed Authentication passed Authentication passed Unsupported OS image.. Jumping nevertheless.. SPL malloc() used 0x1ad8c0 bytes (1718 KB) Authentication passed Authentication passed Starting ATF on ARM64 core... NOTICE: BL31: v2.10.0(release):v2.10.0-367-g00f1ec6b87-dirty NOTICE: BL31: Built : 16:09:05, Feb 9 2024 U-Boot SPL 2024.04-dirty (Dec 05 2024 - 17:48:44 +0800) SYSFW ABI: 4.0 (firmware rev 0x000a '10.0.8--v10.00.08 (Fiery Fox)') SPL malloc() before relocation used 0x2e80 bytes (11 KB) >>SPL: board_init_r() spl_init Trying to boot from MMC2 Authentication passed Authentication passed Jumping to U-Boot... SPL malloc() used 0x12a740 bytes (1193 KB) image entry point: 0x80800000 U-Boot 2024.04-dirty (Dec 05 2024 - 17:48:44 +0800) SoC: AM62AX SR1.0 HS-FS Model: Texas Instruments AM62A7 SK DRAM: 2 GiB (effective 4 GiB) Core: 87 devices, 30 uclasses, devicetree: separate MMC: mmc@fa10000: 0, mmc@fa00000: 1 Loading Environment from nowhere... OK In: serial@2800000 Out: serial@2800000 Err: serial@2800000 Net: eth0: ethernet@8000000port@1 Hit any key to stop autoboot: 1

为什么 SPL 没有输入"board_init_r ()"?

我想我们需要调试方向和建议。

非常感谢

Gibbs