工具与软件:

您好、TI 专家 J ü、

在 AM62D 芯片的上电过程和初始化过程中(包括复位期间)、我们是否可以将音频 McASP 接口的每个引脚配置为输出0电平信号或 Hi-Z?

Tks。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好、Tian Mei

感谢您的提问。

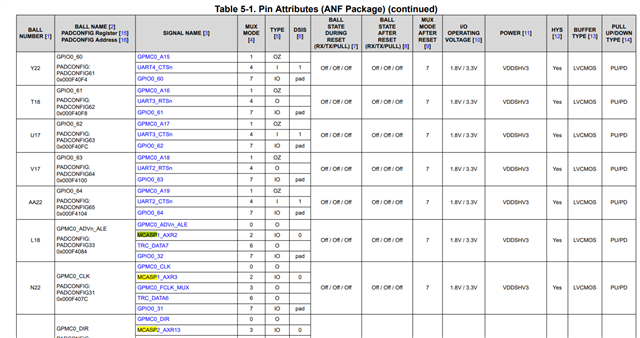

复位期间的大多数 McASP 信号被配置为 GPIO。

复位期间和复位后、TX 和 RX 缓冲器关闭。 禁用内部拉电阻。

IO 实际上处于高阻态。

只有在 ROM 引导完成且软件正在运行后、才能配置 IO。

如果您希望这些 IO 中的任何一个在复位期间和复位后处于已知状态、建议进行外部拉取。

在运行期间、如果这些 IO 中的任何一个可能悬空、建议使用外部拉电阻。

此致、

Sreenivasa

你好、Tian Mei

谢谢你。

请参阅 Am62D-Q1数据表的以下部分

6.8.6 LVCMOS 电气特性

IIN (2)输入漏电流。 VI = 1.8V 10 µA VI = 0V -10 µA

(2)此参数定义了当端子在未启用内部拉电阻的情况下作为输入、未驱动输出或同时作为输入和未驱动输出运行时的漏电流

感谢您的回复。 我们在过去两天进行了一个实验、实际测量了 McASP 接口上的引脚在上电和复位时的电平为0.48v 左右。 复位后、我们配置了 IO 下拉电阻、因此引脚电平将为0v。您认为这个0.48v 电平是正常的吗? [报价]这是一个观察结果还是您有一些疑虑?

此致、

Sreenivasa

你好、Tian Mei

请参阅以下额外输入

未连接的 AM62Dx 引脚上可能存在电压。 在引脚上观察到的电压是 IO 缓冲器中泄漏路径的结果、其中对于 VSS 或 VDDSHV、泄漏电流可能高达10uA。 只要泄漏电流不大于10uA、这是正常的。 只要 IO 缓冲器中的接收器(输入缓冲器)保持关闭、产生的1/2 Vs 电压就不是 AM62Dx 器件的问题。 但是、只要 打开接收器、就必须驱动该引脚或将其拉至有效的逻辑电平。 绝不允许 AM62Dx 器件中已启用的输入缓冲器的输入悬空。

注意:我们建议 对将 AM62Dx 连接到另一个器件输入端的任何信号使用外部上拉电阻。 需要进行外部拉取以将信号保持 在有效逻辑状态、直到软件打开相关的 AM62Dx IO 缓冲器 、以便其 将信号驱动至有效逻辑状态。

此致、

Sreenivasa

你好、Tian Mei

[报价 userid="573771" url="~/support/processors-group/processors/f/processors-forum/1461355/am62d-q1-the-am62d-mcasp-interface-configuration/5616356 #5616356"]如数据表所述、如果泄漏电流小于10uA、则泄漏电压不应为0.48v。 这是正确的吗?正确。 电压取决于泄漏和 IO 电源。

此致、

Sreenivasa