主题中讨论的其他器件: SK-AM64B、 TPS65220

工具与软件:

大家好、团队成员:

我的客户有以下问题。

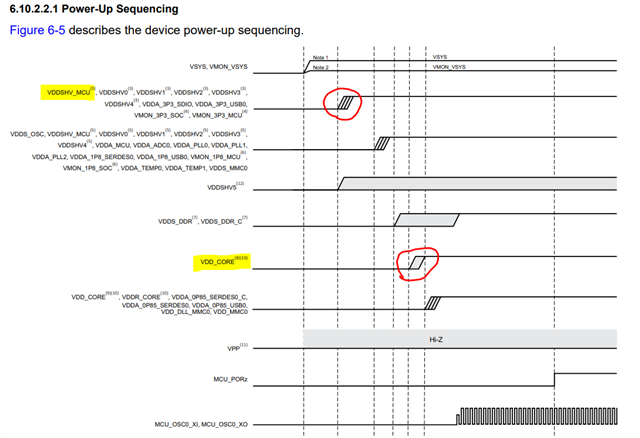

关闭要求是否为以下两点?

- VDDR_CORE 必须在 VDD_CORE 之前断电

- VDDR_CORE 电势绝不能超过 VDD_CORE+018V

因此、可以为电源轨供电 其他 VDDR_CORE、VDDS_DDR 和 VDDS_DDR_C 可以同时断电、或者在 VDD_CORE 之后断电?

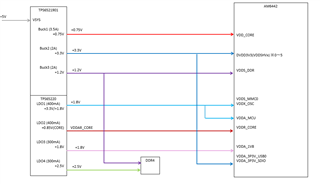

默认情况下、TPS6521901、BUCK1 (+0.75V)的电源序列在 BUCK2 (+3.3V/+1.8V)之后10ms 断电。

但是、我的客户希望为 AM6442的 VDD_CORE 提供 BUCK1、为 VDDSHV (0~5)提供 BUCK2。

VDDSHV 将在 VDD_CORE 之后断电、但这可以吗?

此致、

Mari Tsunoda.