工具与软件:

您好、TI 专家。

我想知道 OSPI DDR 模式时序参数。

以下参数 M / N / T / R 的含义是什么

以及如何找到此参数的值。 我想计算 O2~O6。

M = OSPI_DEV_DELAY_REG[D_INIT_FLD]

N = OSPI_DEV_DELAY_REG[D_AFTER_FLD]

T = OSPI_RD_DATA_CAPTURE_REG[DDR_READ_DELAY_FLD]

R =基准时钟周期时间(以 ns 为单位)

谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好、TI 专家。

我想知道 OSPI DDR 模式时序参数。

以下参数 M / N / T / R 的含义是什么

以及如何找到此参数的值。 我想计算 O2~O6。

M = OSPI_DEV_DELAY_REG[D_INIT_FLD]

N = OSPI_DEV_DELAY_REG[D_AFTER_FLD]

T = OSPI_RD_DATA_CAPTURE_REG[DDR_READ_DELAY_FLD]

R =基准时钟周期时间(以 ns 为单位)

谢谢你。

您好!

[报价用户 id="604835" url="~/support/processors-group/processors/f/processors-forum/1469003/tda4vm-q1-tdav4m-ospi-ddr-mode-parameter "]M = OSPI_DEV_DELAY_REG[D_INIT_FLD]

N = OSPI_DEV_DELAY_REG[D_AFTER_FLD]

T = OSPI_RD_DATA_CAPTURE_REG[DDR_READ_DELAY_FLD]

[报价]这些是为 OSPI 控制器编程的寄存器名称和字段值。

例如、M 是 OSPI0寄存器"OSPI_DEV_DELAY_REG"中字段"D_INIT_FLD"的值@ 0x4704000C。

R 是提供给 OSPI 控制器的参考时钟。

此致、

Tanmay

您好!

REFCLK 与 OSPI 时钟是一样的?

否 REFCLK 是用于 OSPI 控制器数字电路的时钟。 它还用于根据一些分频器设置生成 OSPI 控制器输出时钟。

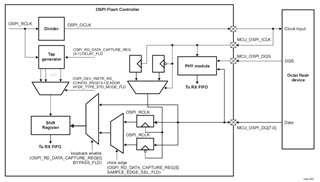

您可以在下图中看到这一点:

此致、

Tanmay