请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS320C6678 工具与软件:

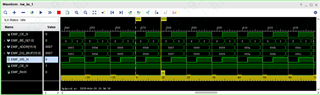

我们使用 TMS320C6678的 EMIF 接口与 FPGA 通信、最大限度地减少 wrSetup、wrStrobe、wrHold、rdSetup、 "读数选通"和"读数提示"。 然而、从 FPGA 捕获的时序来看、当我们被上拉时、删除一个 wrSetup 和 wrHold 周期会导致额外的四个上拉周期。 这是什么原因造成的? 此外、我可以问 EMIF 接口传输的最大数据速率是多少吗?