主题中讨论的其他器件:AM67、 SysConfig

工具与软件:

您好、TI 专家 J ü、

我们正在对 EVM 板上的新 DDR 芯片(Samsung 4G K4FBE3D4HB-KHCT2V)进行调整、但 uboot 采样似乎无法正常启动。

以下是我们采取的一些措施:

请参阅新的 DDR 参数、并使用 DDR 生成工具(SysConfig (TI.com))生成新的 DDR 配置文件。

将 生成的文件重命名为 k3-j722s-ddr-lp4-50-3733.dtsi、并替换原始的 k3-j722s-ddr-lp4-50-3733.dtsi ;

3.修改 k3-j722s-evm.dts 中的内存节点、如下所示

问题:

1. 新的 DDR 参数是如下文件,请帮我检查参数是否正确?

e2e.ti.com/.../TDA4VEntry-DDR-Config-Tool_4D916E7FC2537065_.xlsx

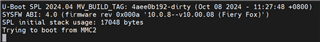

2.为什么 uboot spl 启动失败、如下图所示?

上传生成的文件(使用时、请将其重命名为 settings_info.syscfg):

e2e.ti.com/.../settings_5F00_info.syscfg.txt

此致。