主题中讨论的其他器件: LMK04832

工具与软件:

您好!

我们计划在设计中使用 AFE7950器件。

在数据表中、 下面给出了 SYSREF 要求。

需要三个 SYSREF 脉冲

完全同步设备。28. 这三个脉冲对于同步 N 分频器(如果

逻辑的时钟分频器和 JESD204链路建立。 SYSREF 在启动软件中的用法

TI 提供的 AFE79xx 配置指南中介绍了该流程。 对于每个脉冲、SPI 寄存器锁存器为

编程为高电平、在此之后将捕获第1个 SYSREF 脉冲并且忽略以下脉冲。 SYSREF

然后、需要保持低电平、以便 SPI 锁存器在下一个脉冲期间再次编程为低电平、然后再编程为高电平。 之后

这3个脉冲、TI 建议关闭 SYSREF 或将其保持在低电平、以防止杂散耦合到器件中

进行采样

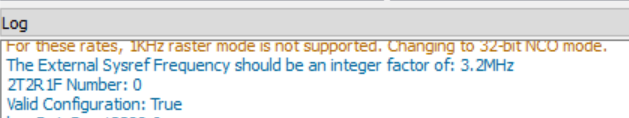

如何计算 SYS-REF 时钟频率范围? 请参阅上述数据表中的"TI 提供了用于计算可能的 SYSREF 频率的 Excel 电子表格"。 请分享电子表格以供参考。

那么 SPI 锁存器与 SYS-REF 信号之间的关系是什么呢? 为什么用 SPI 信号来参考 SYS-REF 信号?

请分享 SYS-REF 信号的详细功能要求?