主题中讨论的其他部件:LMK0.4832万,

您好,我计划在当前项目中使用AFE7950IABJ。 请就以下问题作出澄清。 谢谢你。

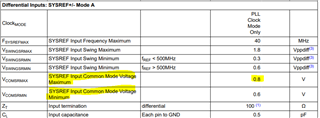

1. REFCLK+/-差分时钟输入 是否在+/-之间具有100欧姆的内部(差分)端接? 数据表指出SYSREF+/-时钟,SYNCBIN+/-和SYNCBOUT+/-信号 的输入/内部端接为100欧姆,但没有REFCLK信息。 这些接口上是否建议使用外部100欧姆电阻器(DNI) ,以防万一?

2.我还打算将TI LMK0.4832万部件用于REFCLK和SYSREF的LVDS时钟输出分配。 这些信号都是0.1 UF交流耦合的,这是一种公平的方法,还是也应该推荐上拉/下拉规定(例如50欧姆电阻器)?

3.如果我 想通过使用SPI配置在睡眠模式下操作AFE7950,是否仍建议在 睡眠GPIO信号上提供硬接线上拉/下拉电压为1.8V (安装下拉电压以保持默认状态)?

4. ALARM1/2输出是否有推荐的默认设置(上拉/下拉),或者如果我可以通过SPI进行配置,是否需要这些设置?